Safinaz Volpe

Francesco P. Volpe

# AVR-MIKROCONTROLLER- PRAXIS

Befehlssatz, Tools

und Anwendungen

Bei der AVR-Familie von Atmel handelt es sich um 8-Bit Mikrocontroller mit RISC-Architektur für die unterschiedlichsten Anwendungen. Der Programmcode wird in einem FLASH-Speicher abgelegt, so daß auch eine In-Circuit-Programmierung möglich ist.

Dieses Buch beschreibt die Architektur und die Peripherie der AVR-Mikrocontroller. Ferner wird der komplette Befehlssatz übersichtlich dargestellt und anschaulich erklärt. Neben Softwaretools, wie Assembler und Simulator, werden auch die für den Entwurf notwendigen Hardwaretools, wie Programmiergerät und Emulator, vorgestellt. Anschließend wird eine AVR-Experimentierplatine besprochen. Das Programmiergerät und die AVR-Experimentierplatine sind als Bausatz erhältlich, so daß der Leser einen schnellen Einstieg in die Programmierung der AVR-Mikrocontroller erhält. Abgeschlossen werden die Betrachtungen mit fertigen Software-Routinen, die z. B. die Ansteuerung von seriellen EEPROMs und einer LCD-Anzeige erlauben.

Das Buch gliedert sich in:

- Aufbau der AVR-Mikrocontroller-Familie und Befehlssatz

- Softwaretools (Assembler und Simulator)

- Hardwaretools (Programmiergerät und Emulator)

- Anwendungen (I2C-Bus, LCD-Anzeige, RS232, CRC-8 u.v.m.)

Dem Buch liegt eine CD mit Assembler, Simulator und den Datenblättern von Atmel, sowie dem Sourcecode der erläuterten Anwendungsbeispielen bei.

M. Eng. Sc., Dipl.-Ing. Safinaz Volpe studierte an den Universitäten Kassel und Melbourne Elektrotechnik. Anschließend war sie eine Zeit lang als Redakteurin bei einer Elektronikzeitschrift tätig.

Prof. Dr.-Ing. Francesco P. Volpe studierte an der Ruhr-Universität Bochum Elektronik. Anschließend promovierte er an der Universität Kassel. Derzeit ist er Professor für Mikrocomputertechnik an der Fachhochschule in Aschaffenburg.

Elektor-Verlag, Aachen

ISBN 3-89576-063-3

ELEKTOR

AVR-MIKROCONTROLLER-PRAXIS

Safinaz Volpe

Francesco P. Volpe

# AVR-MIKROCONTROLLER- PRAXIS

Befehlssatz, Tools

und Anwendungen

ELEKTOR

Safinaz Volpe

Francesco P. Volpe

# AVR-Mikrocontroller-Praxis

Befehlssatz, Tools und Anwendungen

2. Auflage

Elektor-Verlag

© 1999 Elektor-Verlag GmbH, 52072 Aachen

2. Auflage 2001

Alle Rechte vorbehalten

Die in diesem Buch veröffentlichten Beiträge, insbesondere alle Aufsätze und Artikel sowie alle Entwürfe, Pläne, Zeichnungen, Illustrationen und Programme sind urheberrechtlich geschützt. Sie dürfen weder teilweise noch vollständig ohne schriftliche Genehmigung des Herausgebers kopiert, gespeichert oder in irgendeiner anderen Weise, sei es elektronisch, mechanisch, gedruckt, fotografiert oder mikroverfilmt, veröffentlicht werden.

Die Informationen im vorliegenden Buch werden ohne Rücksicht auf einen eventuellen Patentschutz veröffentlicht. Die in diesem Buch erwähnten Soft- und Hardwarebezeichnungen können auch dann eingetragene Warenzeichen sein, wenn darauf nicht besonders hingewiesen wird. Sie gehören den jeweiligen Warenzeicheninhabern und unterliegen gesetzlichen Bestimmungen.

Bei der Zusammenstellung von Texten und Abbildungen wurde mit größter Sorgfalt vorgegangen. Trotzdem können Fehler nicht vollständig ausgeschlossen werden. Verlag, Herausgeber und Autor können für fehlerhafte Angaben und deren Folgen weder eine juristische Verantwortung noch irgendeine Haftung übernehmen. Für die Mitteilung eventueller Fehler sind Verlag und Autor dankbar.

Umschlaggestaltung: Ton Galikers, Segment, Beek (NL)

Graphische Gestaltung: Laurent Martin, Hans Koerfer-Bernstein

Satz und Aufmachung: TechKnow, Hans Koerfer-Bernstein, Aachen

Belichtung: typeline, Aachen und TechKnow, Hans Koerfer-Bernstein, Aachen

Druck: Giethoorn/TenBrink, Meppel, Niederlande

Printed in the Netherlands

ISBN 3-89576-063-3

Elektor-Verlag, 52072 Aachen

989009

Der Elektor-Verlag ist Mitglied der

Verlagsgruppe Segment B.V. (Niederlande)

Wir widmen dieses Buch unserer Tochter

Sarah Safinaz

## Inhaltsverzeichnis

|                                                |    |

|------------------------------------------------|----|

| 1 Einleitung                                   | 7  |

| 2 Die AVR-Mikrocontroller-Familie              | 9  |

| 2.1 Eigenschaften und Typen                    | 9  |

| 2.2 AVR-Architektur                            | 12 |

| 2.3 Speicher und Register                      | 14 |

| 2.3.1 Programmspeicher                         | 14 |

| 2.3.2 Datenspeicher (SRAM)                     | 16 |

| 2.3.3 EEPROM                                   | 17 |

| 2.3.4 General Purpose Register                 | 18 |

| 2.3.5 I/O-Register                             | 20 |

| 2.3.6 STATUS-Register                          | 22 |

| 2.4 Peripherie                                 | 23 |

| 2.4.1 I/O-Ports                                | 23 |

| 2.4.2 Synchrone serielle Schnittstelle (SPI)   | 24 |

| 2.4.3 Asynchrone serielle Schnittstelle (UART) | 26 |

| 2.4.4 Analog-Komparator                        | 29 |

| 2.4.5 Analog/Digital-Wandler                   | 30 |

| 2.4.6 Timer und Counter                        | 32 |

| 2.4.7 Watchdog-Timer                           | 38 |

| 2.5 Stack                                      | 38 |

| 2.5.1 Hardware-Stack                           | 40 |

| 2.5.2 Stack im Datenspeicher                   | 40 |

| 2.6 Reset                                      | 41 |

| 2.7 Reset und Interrupt-Vektoren               | 42 |

| 2.8 Taktoszillator                             | 43 |

| 2.8.1 Quarz-Oszillator                         | 43 |

| 2.8.2 Externer Takt                            | 43 |

| 2.8.3 Interner RC-Oszillator                   | 44 |

| 2.9 Der Befehlssatz                            | 45 |

|                                                   |     |

|---------------------------------------------------|-----|

| 3 Software-Entwicklungstools                      | 167 |

| 3.1 AVR-Assembler                                 | 167 |

| 3.1.1 Direktiven                                  | 169 |

| 3.1.2 Kommentare                                  | 170 |

| 3.1.3 Ausdrücke                                   | 171 |

| 3.1.4 Symbole und Marken                          | 172 |

| 3.1.5 Datentypen                                  | 174 |

| 3.1.6 Funktionen                                  | 175 |

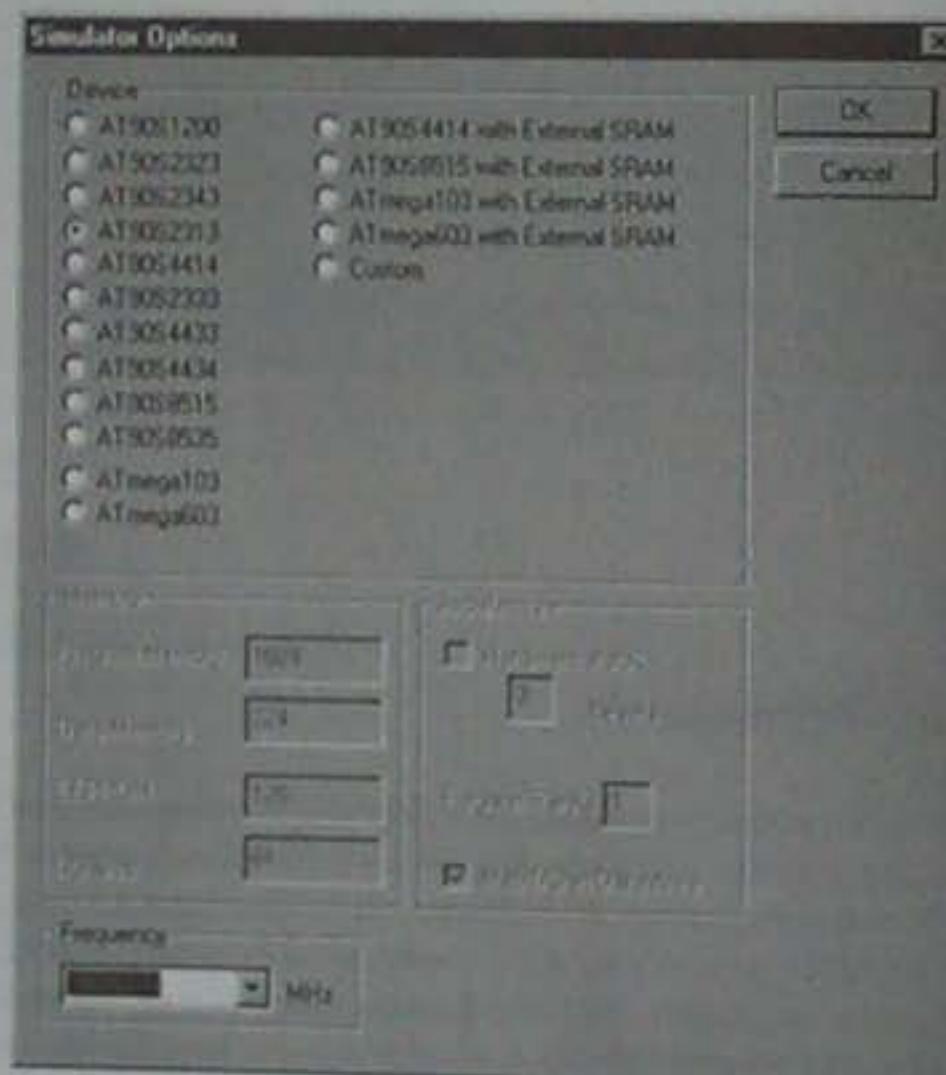

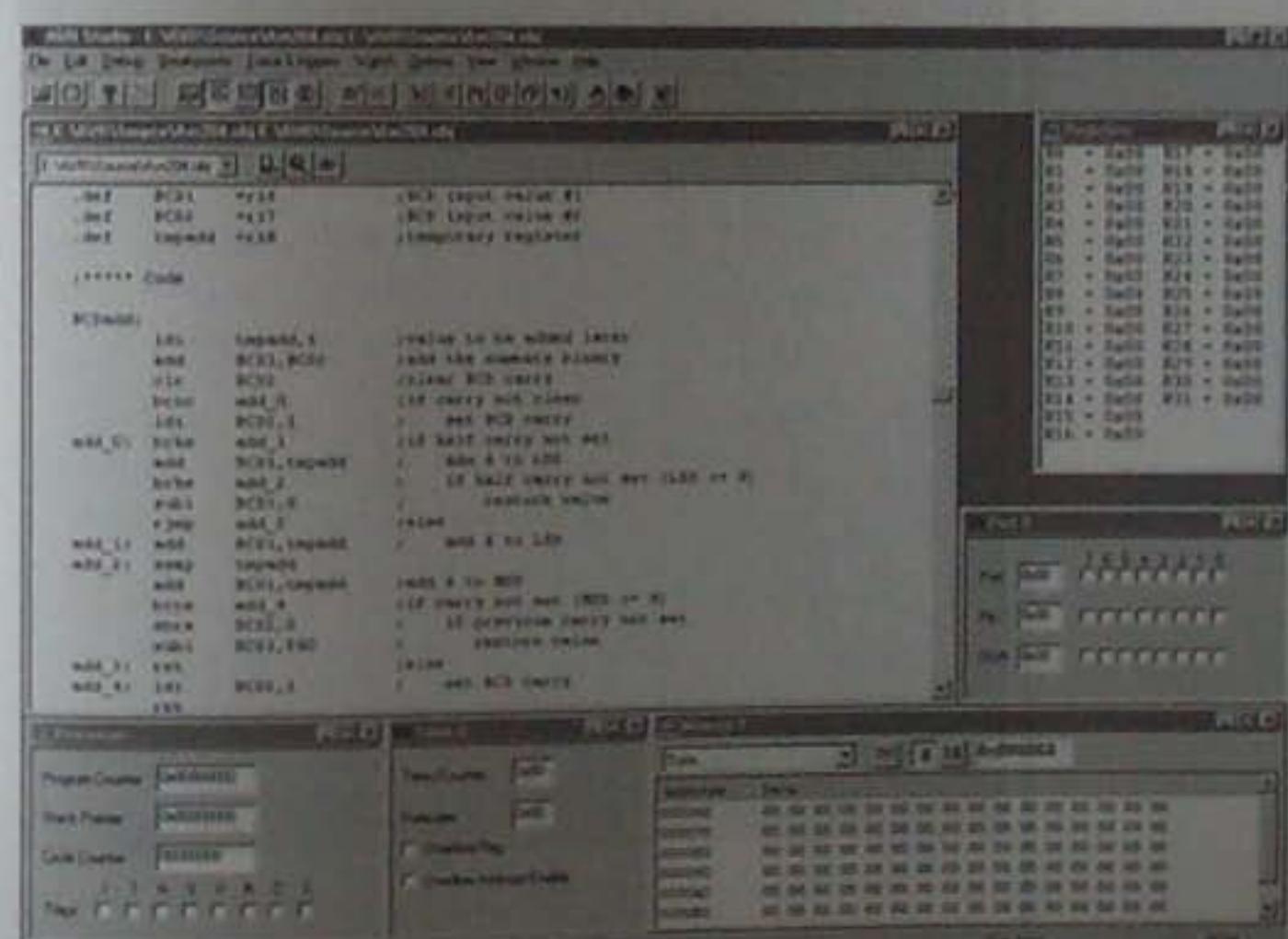

| 3.2 AVR-Simulator                                 | 175 |

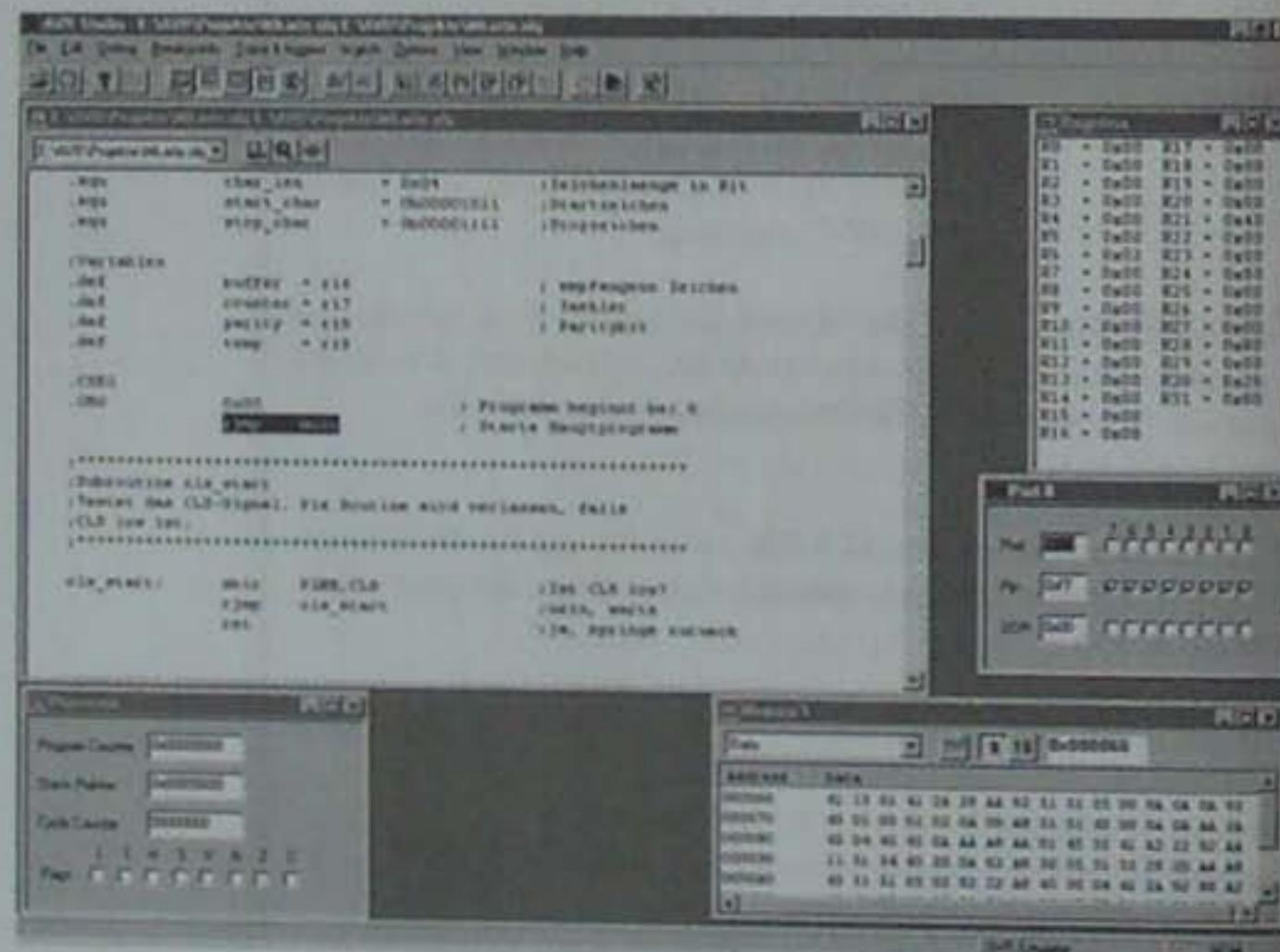

| 3.3 AVR-Studio                                    | 176 |

| 4 Hardware-Entwicklungstools                      | 181 |

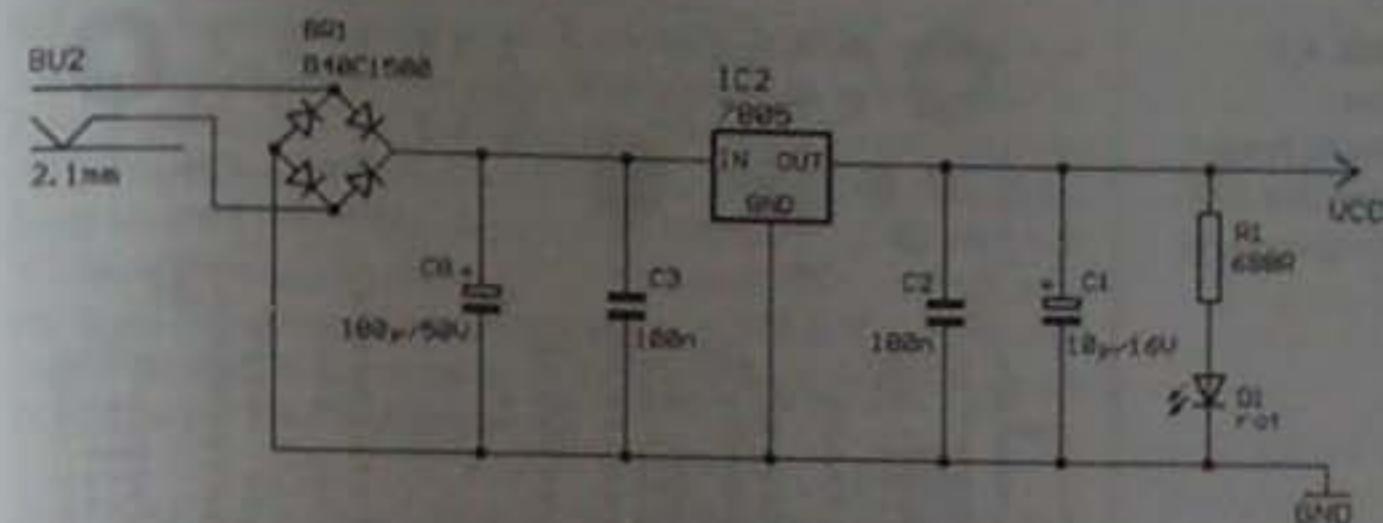

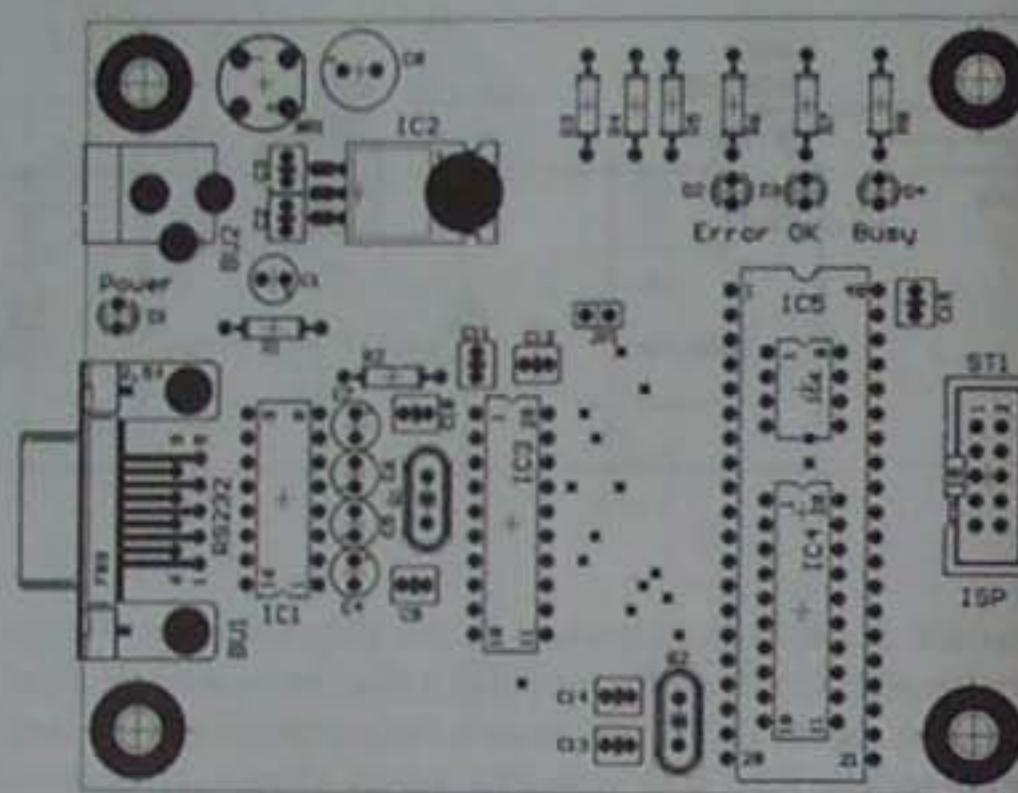

| 4.1 AVR-Programmer                                | 181 |

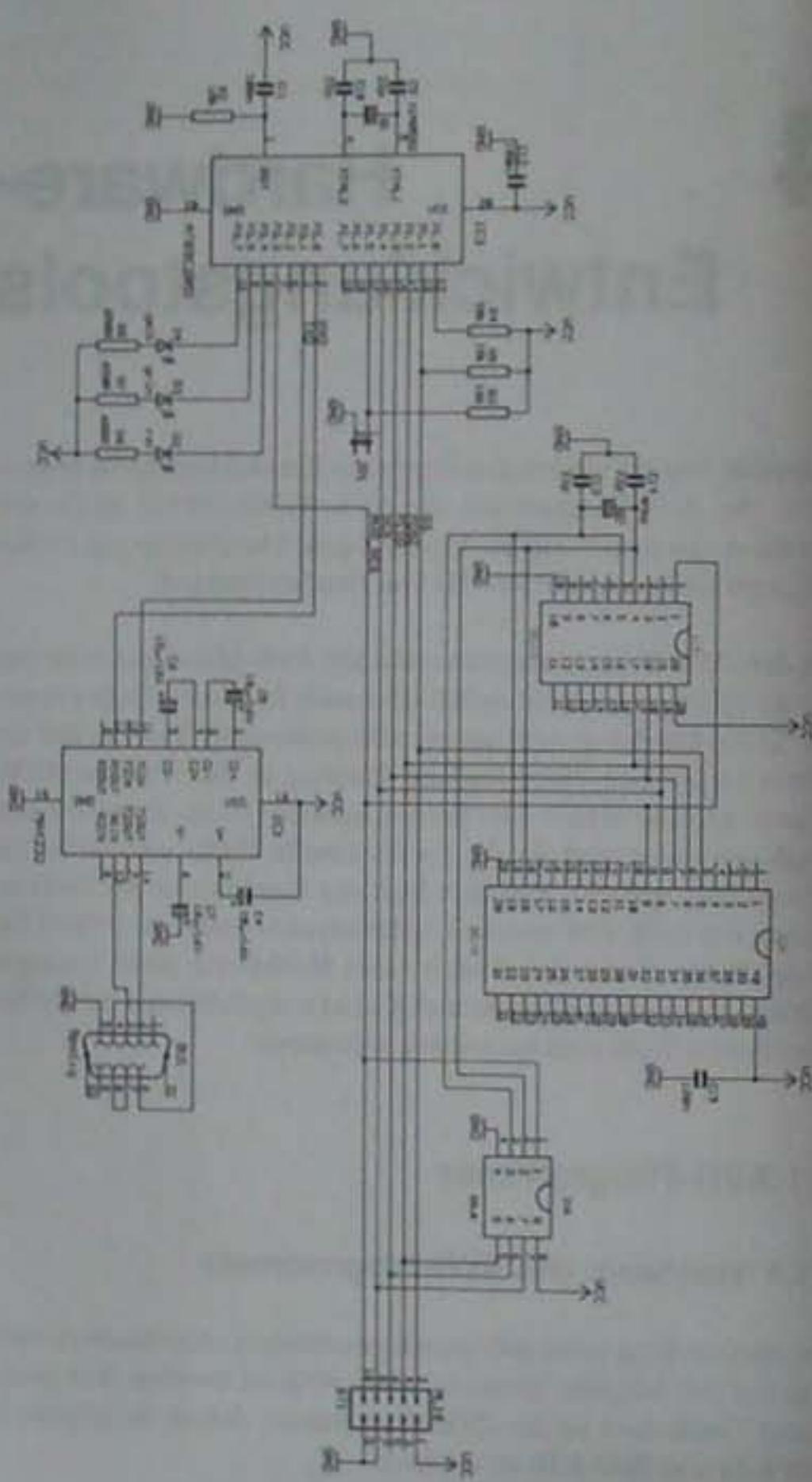

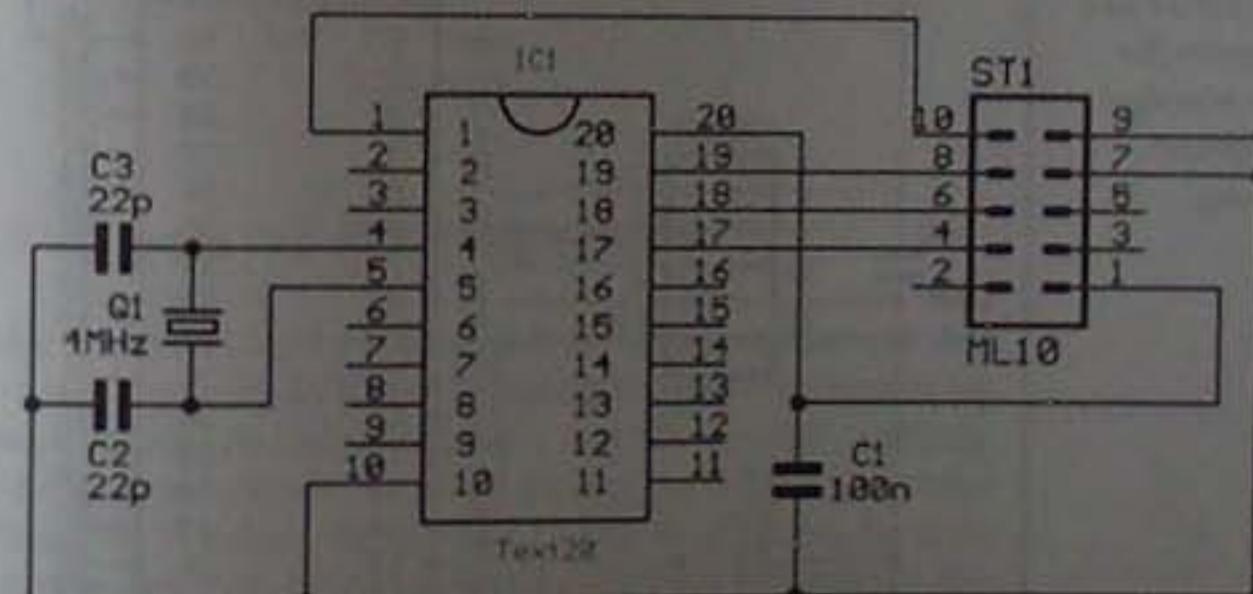

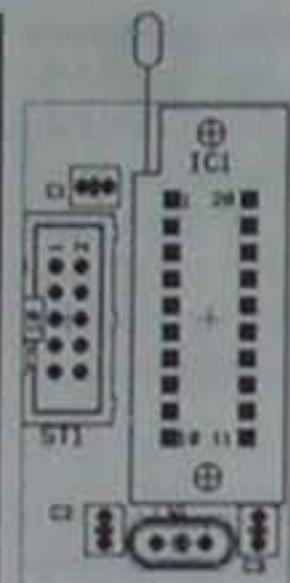

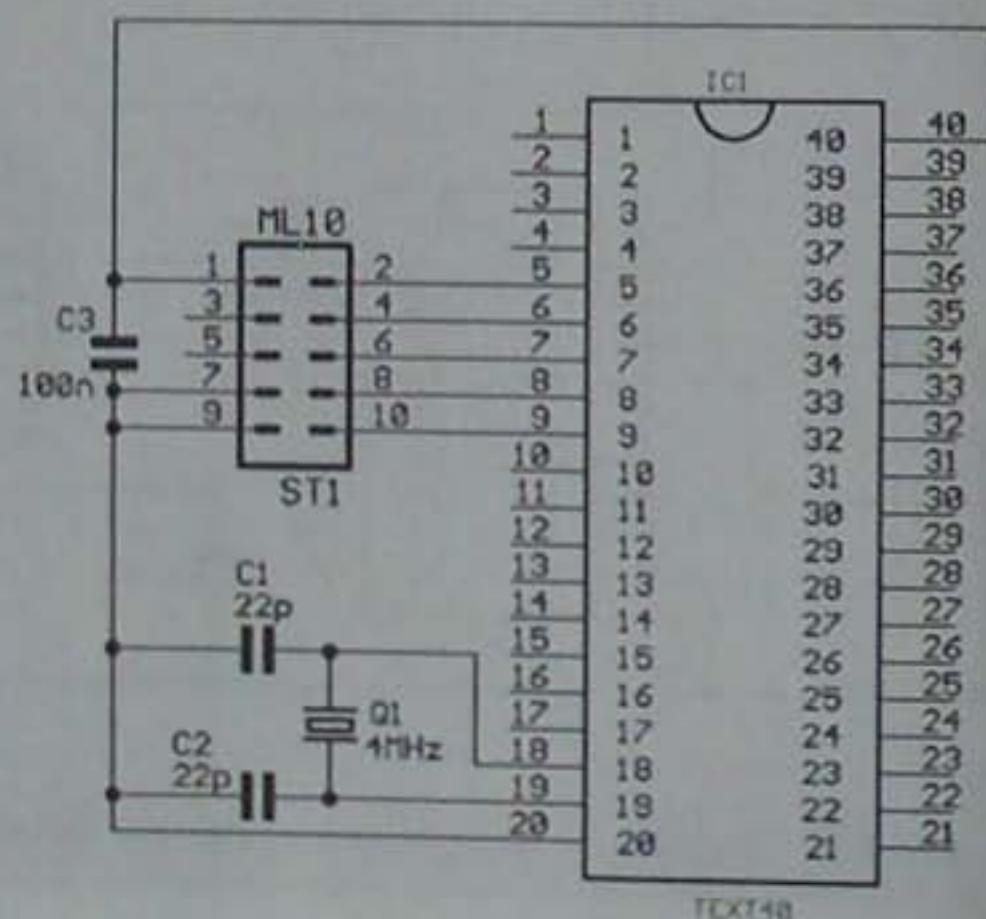

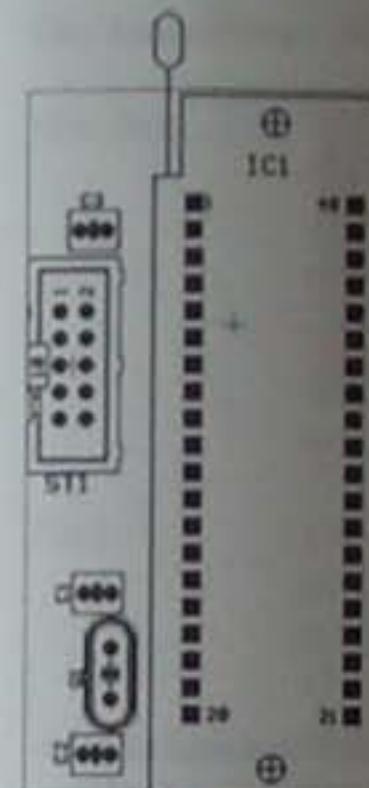

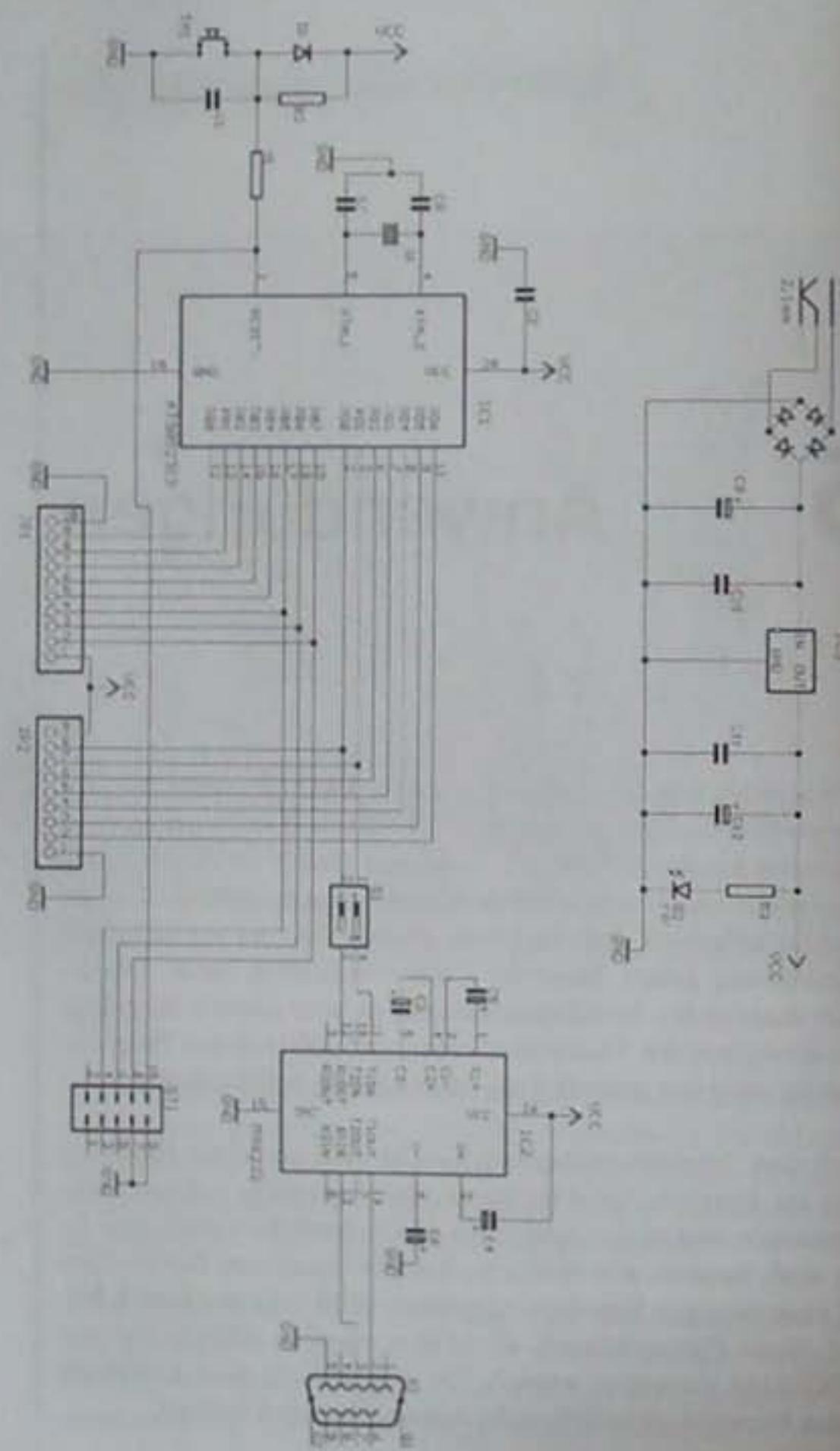

| 4.1.1 Hardware des AVR-Programmers                | 181 |

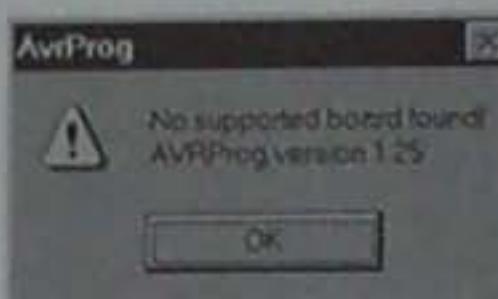

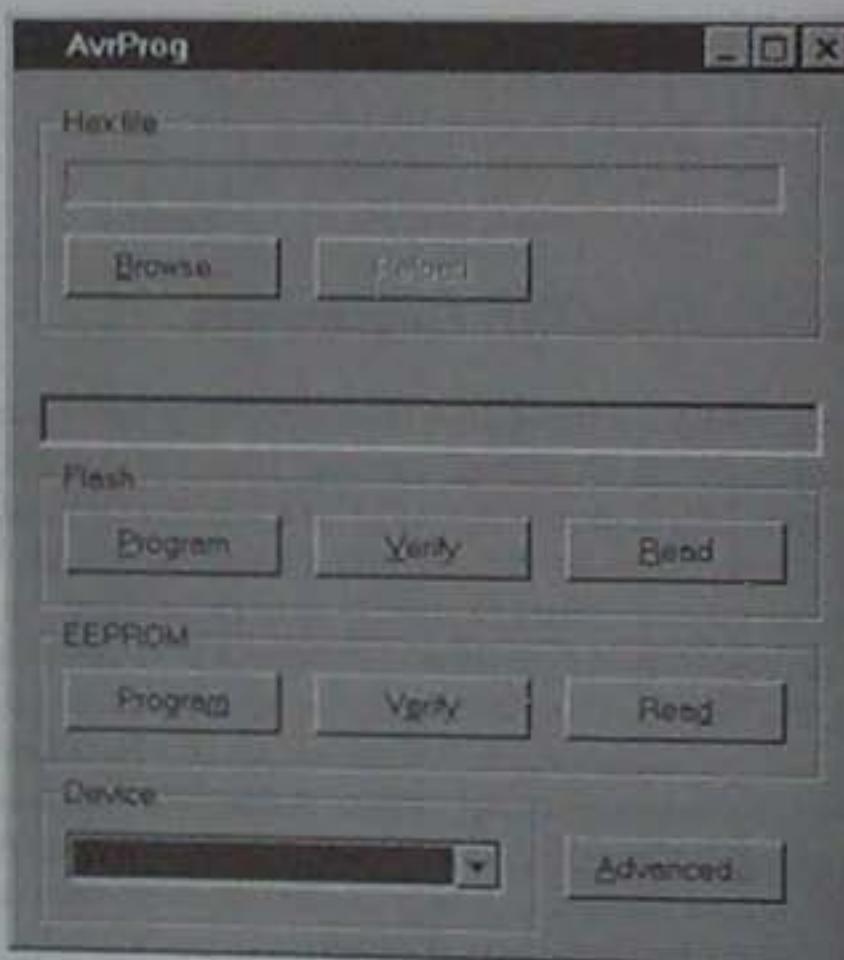

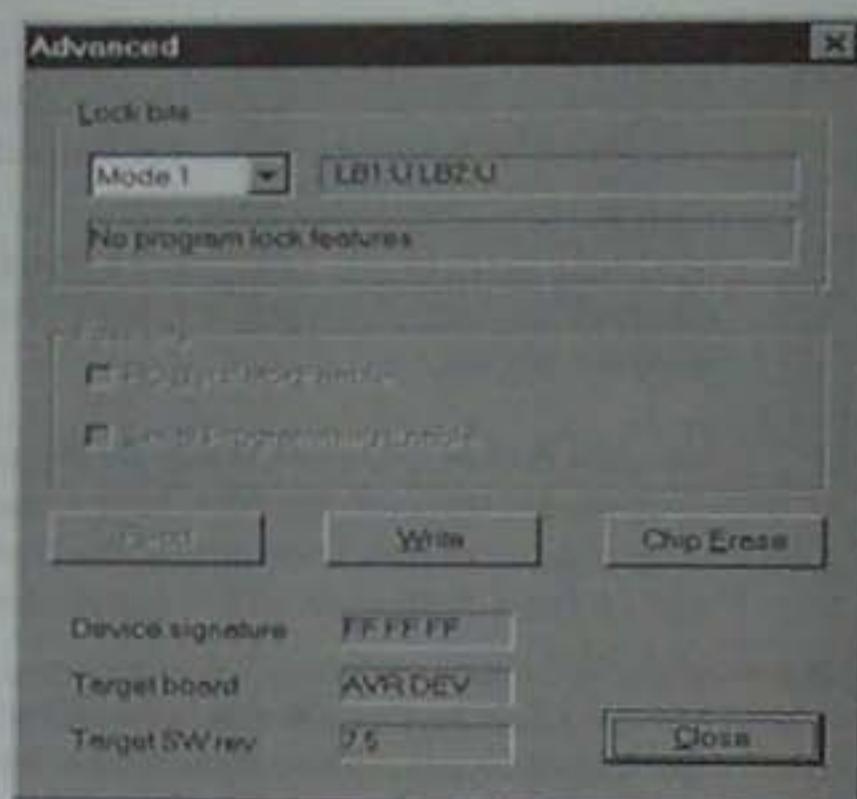

| 4.1.2 Software des AVR-Programmers                | 187 |

| 4.2 Der Emulator AVR AT90ICEPRO                   | 192 |

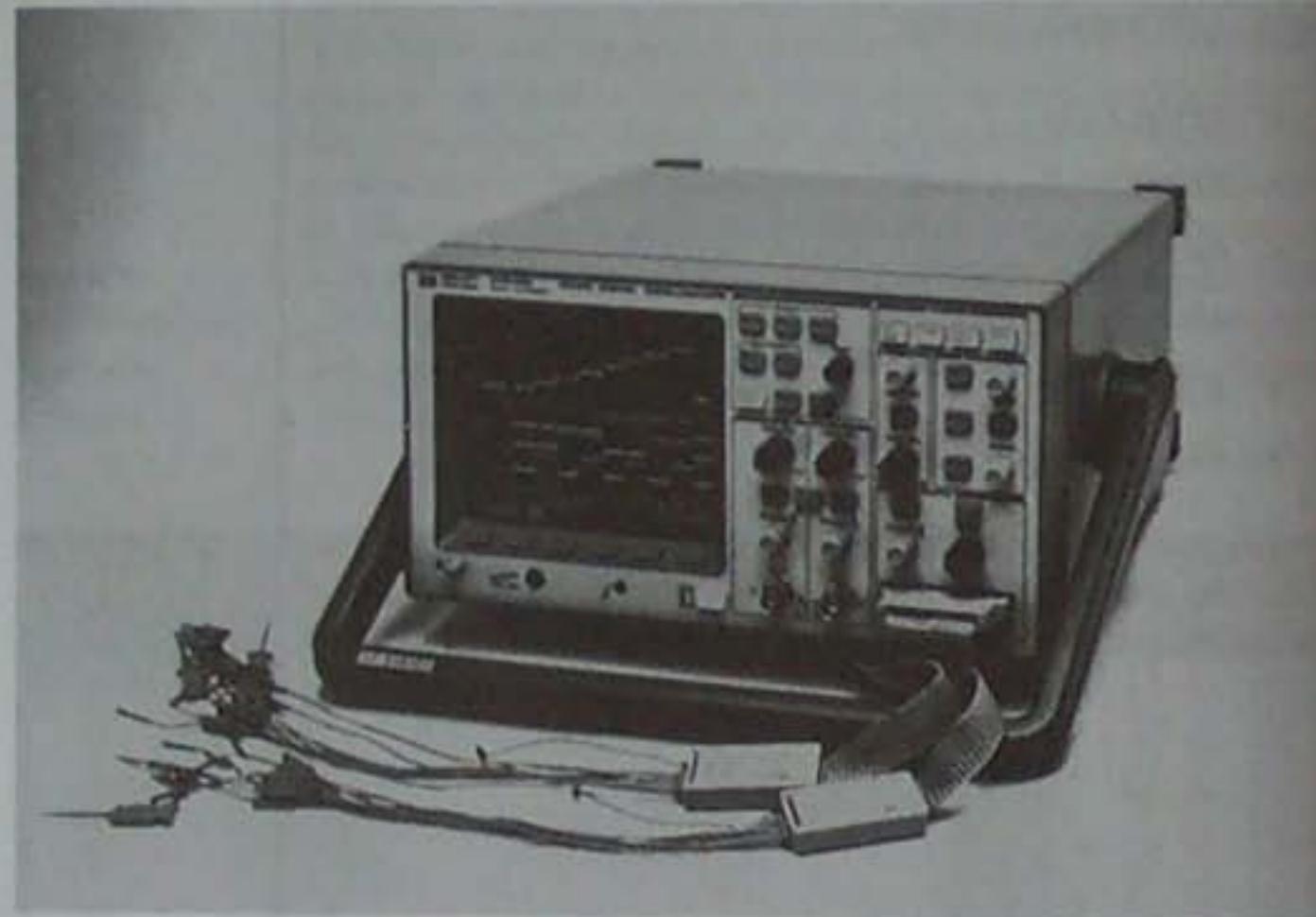

| 4.3 Logikanalysator HP54645D                      | 194 |

| 5 Anwendungen                                     | 195 |

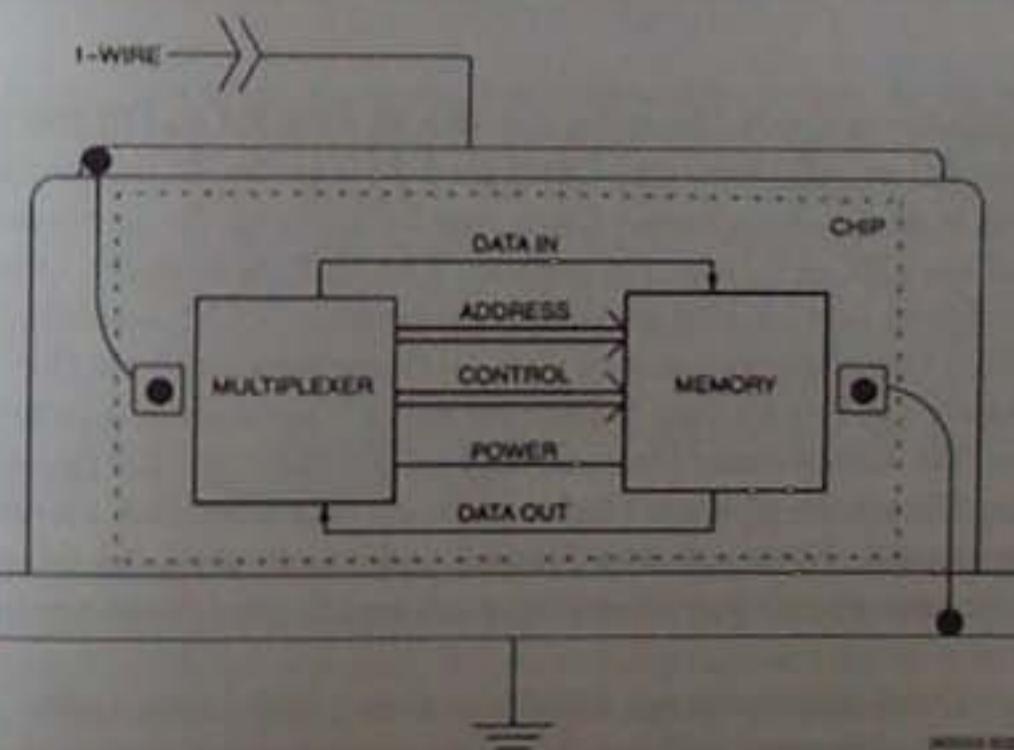

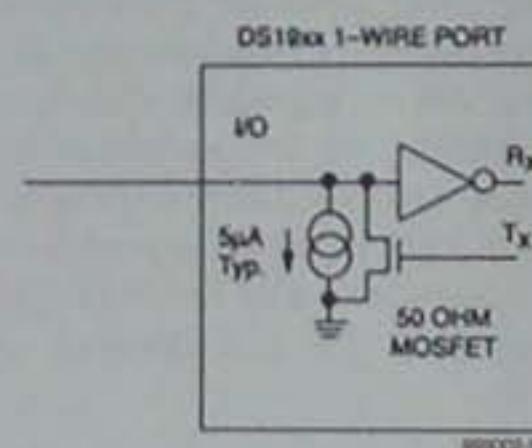

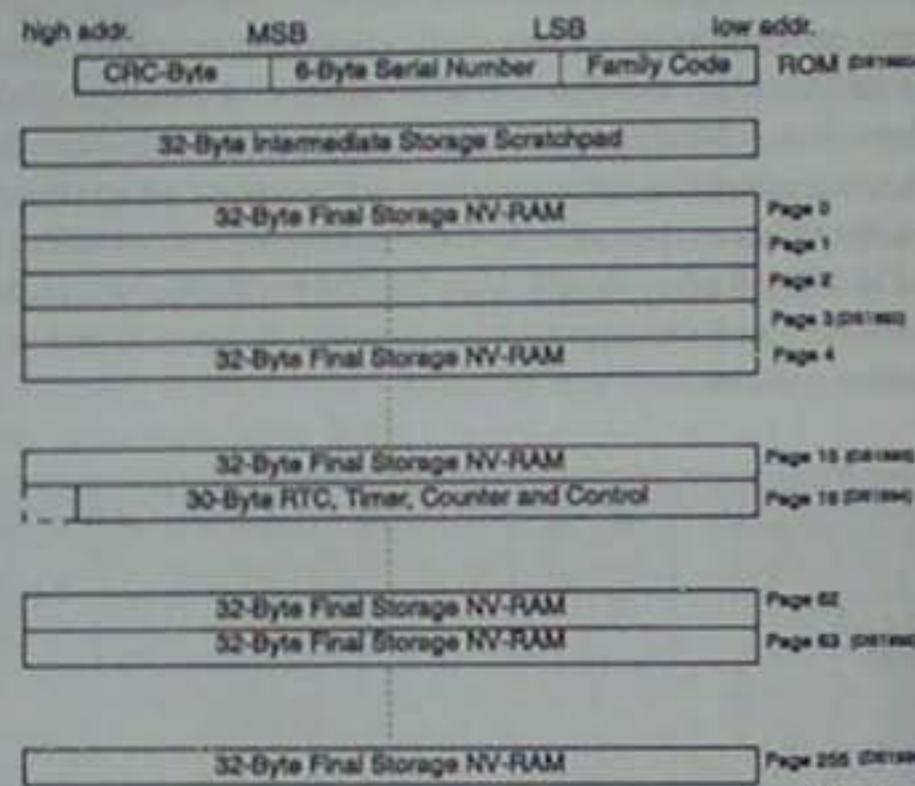

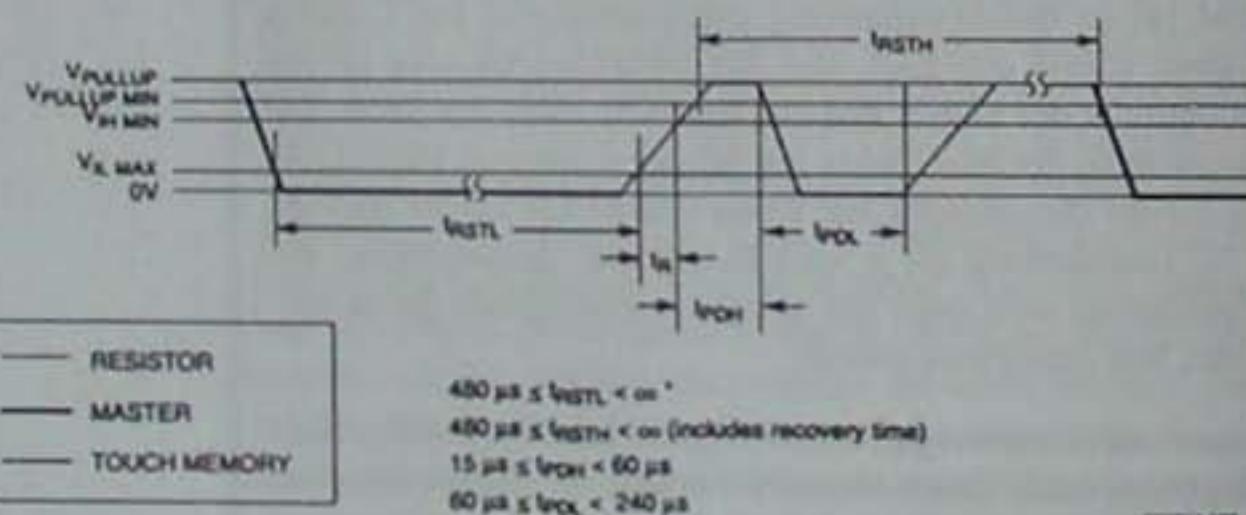

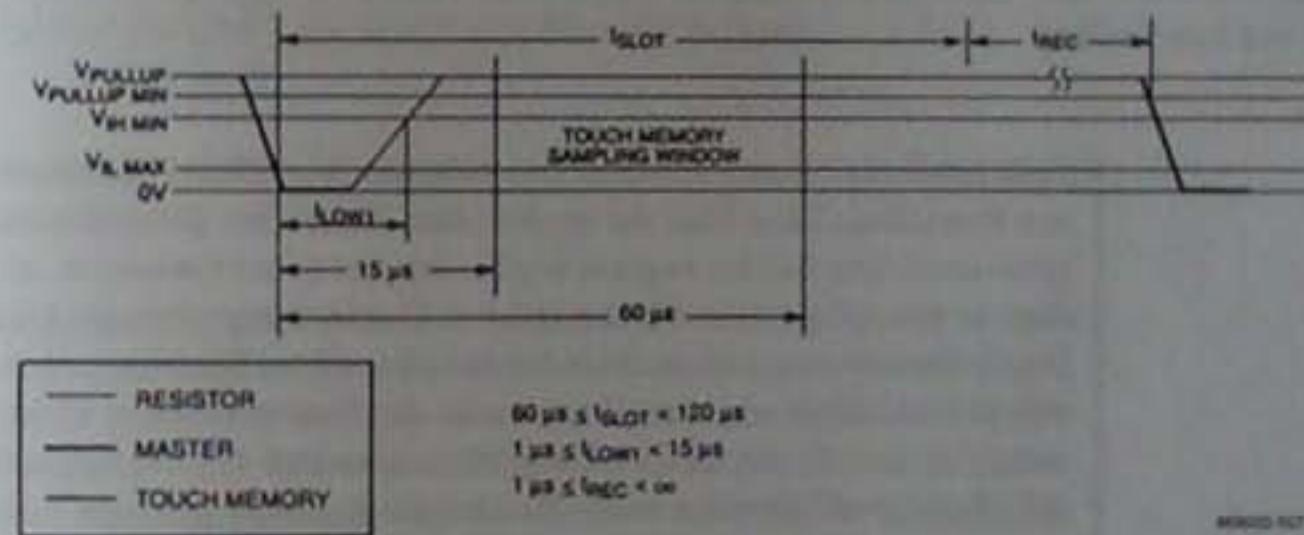

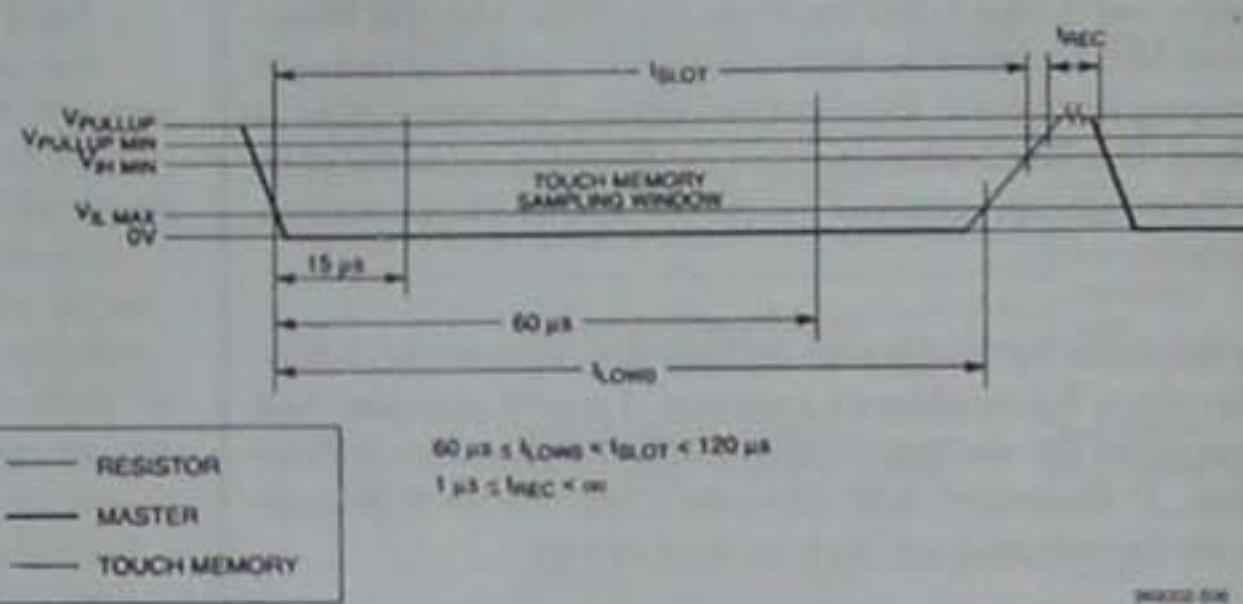

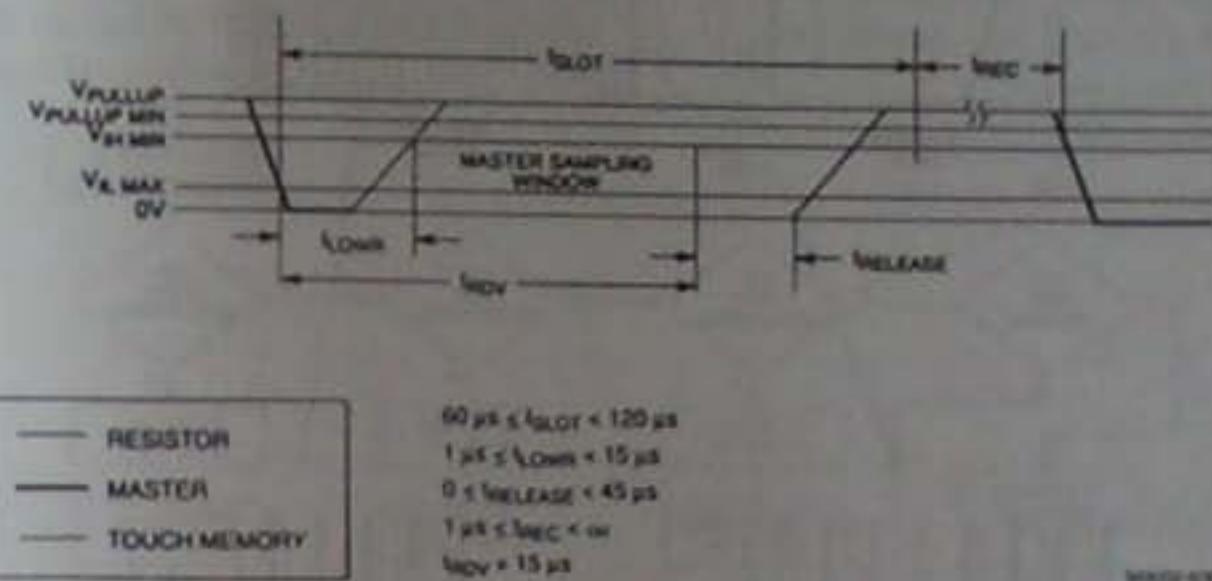

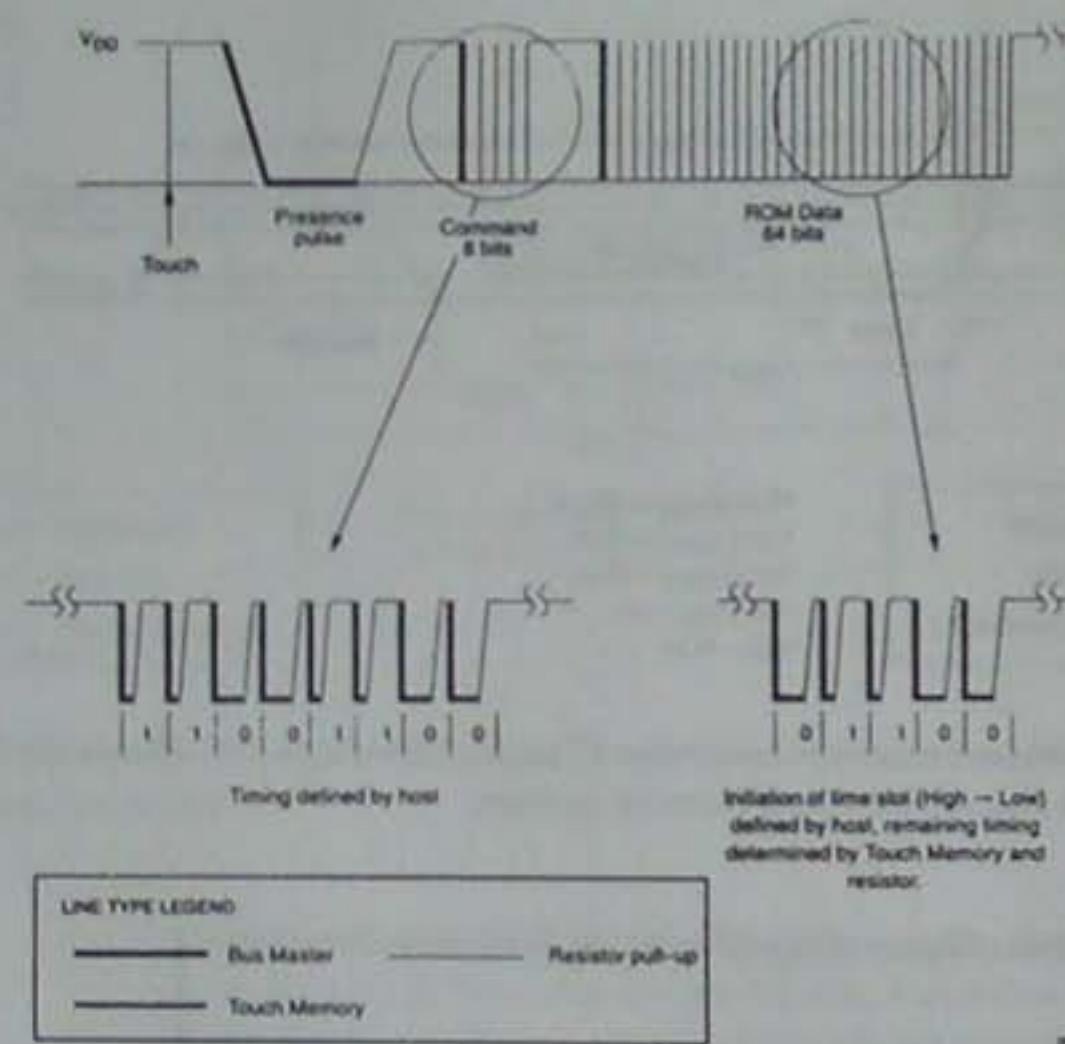

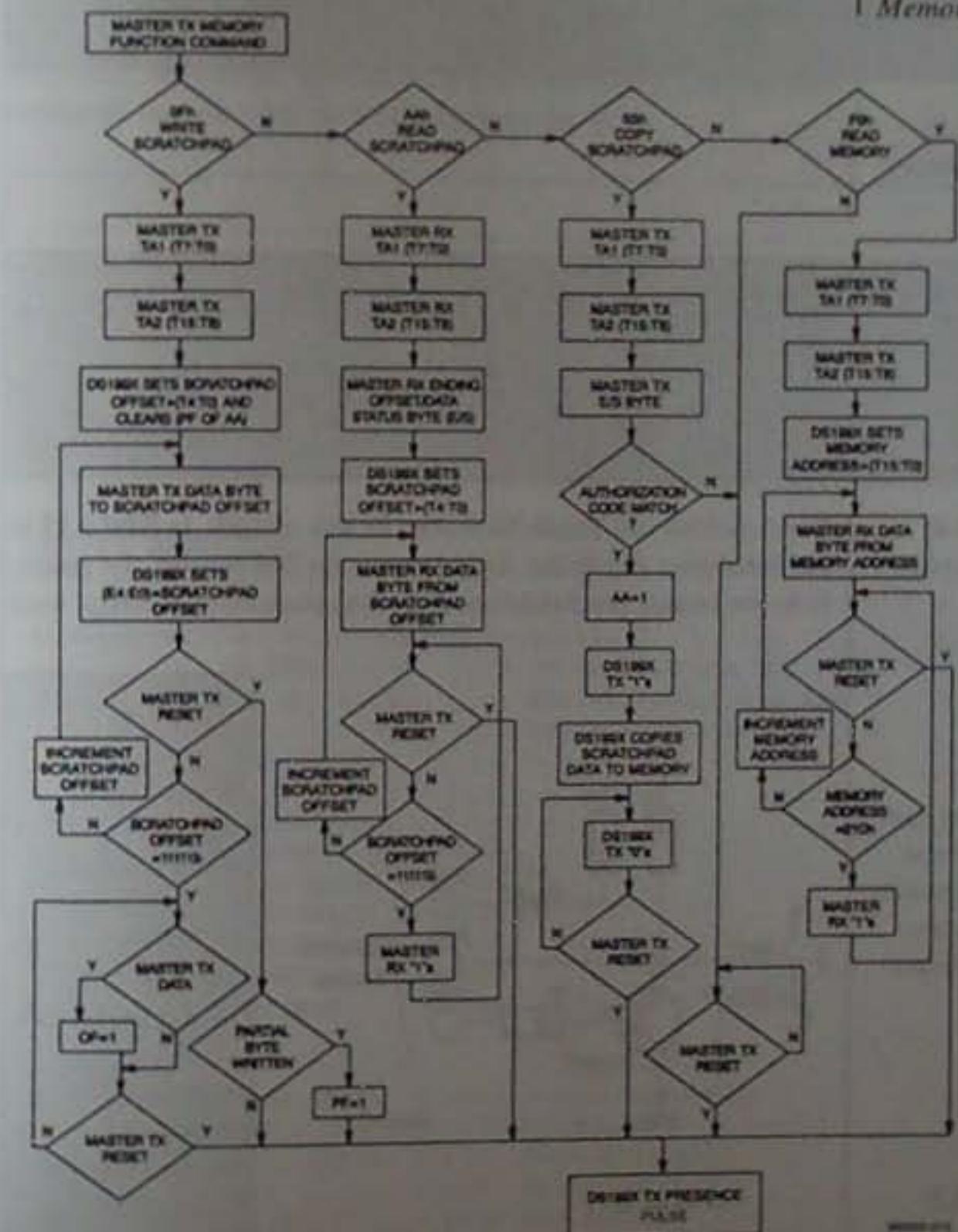

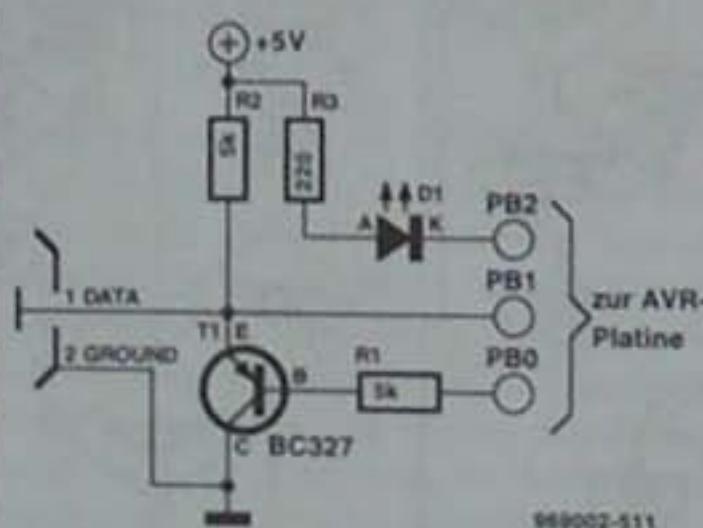

| 5.1 Touch-Memories                                | 199 |

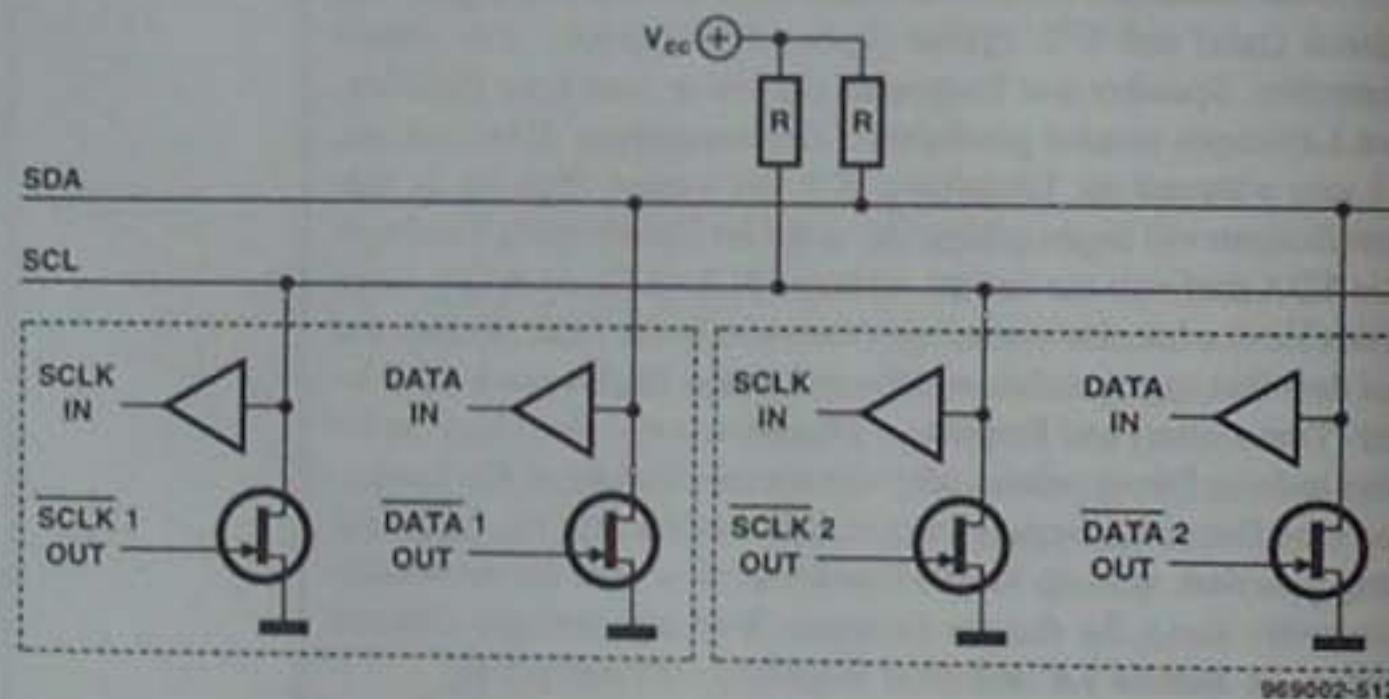

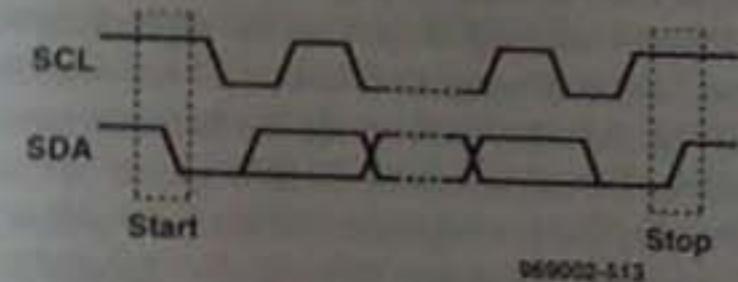

| 5.2 Ansteuerung von EEPROMs mit I2C-Bus-Protokoll | 215 |

| 5.3 Ansteuerung einer LCD-Anzeige                 | 229 |

| 5.4 Telefonkartenleser                            | 240 |

| 5.5 Magnetkartenleser                             | 248 |

| 5.6 Serielle Kommunikation                        | 261 |

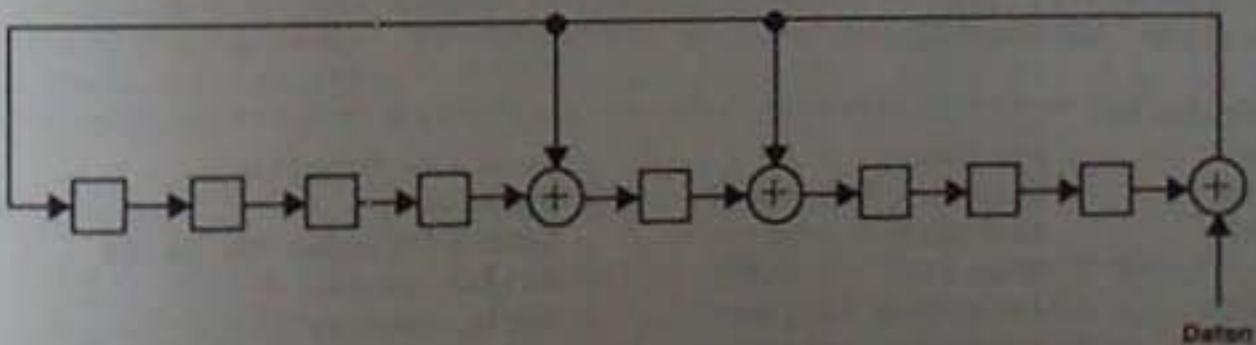

| 5.7 Cyclic Redundancy Check (CRC)                 | 268 |

| Anhang                                            | 273 |

| A.1 Inhalt der CD                                 | 273 |

| A.2 Bezugsquellen                                 | 277 |

| A.3 Literaturverzeichnis                          | 281 |

| Stichwortverzeichnis                              | 283 |

**Vorwort**

Dieses Buch beschreibt die AVR-Mikrocontroller-Familie der Firma Atmel. Es gibt eine kurze Einführung in die Architektur der AVR-Mikrocontroller und beschreibt die Peripherie-Module und Eigenschaften dieser Controller. Großen Raum nimmt die Beschreibung des Befehlssatzes ein. Die Datenblätter aller in diesem Buch beschriebener AVR-Mikrocontroller sowie zahlreiches Informationsmaterial von der Atmel Home Page befinden sich als PDF-File auf der beiliegenden CD.

Die zum Einstieg notwendigen Softwaretools, wie Assembler und AVR-Studio (Simulator) werden vorgestellt und befinden sich ebenfalls auf der CD. Der vorgestellte AVR-Programmer und die Experimentierplatine kann der interessierte Leser beim Elektronik Laden in Detmold (siehe Anhang) erwerben. Damit sollte der schnelle Einstieg in die Programmierung der AVR-Mikrocontroller keinerlei Schwierigkeiten bereiten. Um den Einstieg noch weiter zu vereinfachen, werden insgesamt sieben Anwendungen ausführlich besprochen. Die benötigten Sourcecodes sind abgedruckt und als Assembler-Dateien auf der CD abgelegt.

Für die freundliche Unterstützung bei der Erstellung des Manuskripts, der Programme und der Platinen bedanken wir uns bei den Firmen Beta-Layout und Cadsoft, bei Bob Henderson und Peter Jones von Atmel in England, bei Herrn Becker von Ineltek in Heidenheim, bei Herrn Yahya vom Ingenieurbüro Yahya in Erkelenz und Herrn Kausler von Hewlett-Packard in Böblingen.

Dem Elektor-Verlag sind wir für die Annahme und Veröffentlichung dieses Buches sehr dankbar. Insbesondere bedanken wir uns bei Herrn Krings und Herrn Klein für die gute Zusammenarbeit und deren Geduld mit uns.

Deisenhofen, im Frühjahr 1999

Safinaz Volpe, Francesco P. Volpe

**1**

# Einleitung

Bei der AVR-Mikrocontroller-Familie von Atmel handelt es sich um 8-Bit Mikrocontroller mit RISC-Architektur (Reduced Instruction Set Computer) für die unterschiedlichsten Anwendungen. Schon bei der Entwicklung der AVR-Mikrocontroller hat Atmel sehr eng mit Herstellern von Hochsprachen-Compilern zusammengearbeitet, um die Architektur und den Befehlssatz für den compilierten C-Code so effizient wie möglich zu gestalten. Dieses Buch beschreibt die Architektur der AVR-Mikrocontroller, die Software- und Hardware-Entwicklungstools sowie sieben ausführlich beschriebene Anwendungen.

In Kapitel 2 wird eine kurze Einführung in die AVR-Mikrocontroller-Architektur gegeben. Es werden alle bis zur Drucklegung dieses Buches verfügbaren Mikrocontrollertypen dieser Familie mit ihren Eigenschaften angegeben. Anschließend werden die implementierten Peripherie-Module kurz vorgestellt. Abgeschlossen wird dieses Kapitel mit einer ausführlichen Erläuterung des AVR-Mikrocontroller-Befehlssatzes. Als Ergänzung und als weiterführende Literatur befinden sich die kompletten Datenblätter aller in diesem Buch vorgestellten AVR-Mikrocontroller als PDF-Datei auf der Begleit-CD.

Die zur Programmentwicklung benötigten Software-Tools werden in Kapitel 3 vorgestellt. Der Atmel AVR-Assembler wird in zwei Version, eine für MS-DOS und eine für Microsoft Windows, ausgeliefert. Dieser Assembler wandelt die Mnemonics in Maschinencode um, der dann in die AVR-Mikrocontroller programmiert werden kann.

Zur vorherigen Simulation des Assembler-Programms hat Atmel einen Simulator angeboten. Dieser Simulator wird nun nicht mehr unterstützt und ist von dem Software-Tools AVR-Studio abgelöst worden. Mit dem AVR-Studio kann der Anwender sowohl das Programm simulieren, er kann aber auch, falls er einen AVR-Emulator AT90ICEPRO besitzt, zur Ansteuerung des Emulators hernehmen. Sowohl der AVR-Assembler, als das AVR-Studio-Simulations-/Emulatorprogramm befinden sich auf der Begleit-CD.

Für den Einstieg mit neuen Mikrocontrollern ist ein dazugehöriges Programmiergerät unumgänglich. Damit der interessierte Leser ein einfaches und preiswertes Programmiergerät für die AVR-Mikrocontroller erhält, wird in Kapitel 4 ein solches Gerät samt der benötigten PC-Software vorgestellt. Diesen AVR-Programmer kann der Leser selber nachbauen oder beim Elektronik Laden in Detmold (siehe Anhang A.2) bestellen. Für die gehobenen Ansprüche bei der Programmierung wird der AVR In-Circuit Emulator AT90ICEPRO vorgestellt. Für ein solches Hardware-Tool muß man zwar leider einige tausend DM bezahlen, aber es macht sich für den professionellen Entwickler sehr schnell bezahlt.

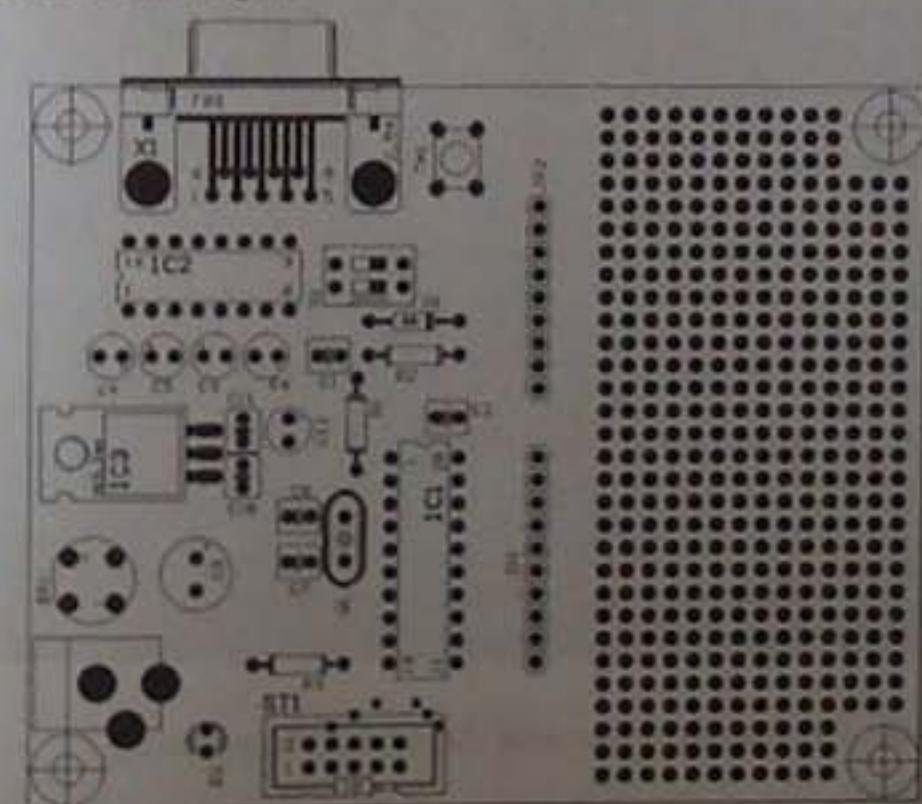

Nichts erklärt einen Sachverhalt besser als ein Beispiel. Aus diesem Grund sind in Kapitel 5 insgesamt sieben unterschiedliche Anwendungen aufgelistet. Jede Anwendung wird ausführlich beschrieben und der dokumentierte Assembler-Sourcecode wird angegeben. Dieser ist auch als Datei auf der Begleit-CD zu finden. Mikrocontroller bilden meist eine Schnittstelle zwischen dem Menschen und einem Gerät oder einer Maschine. Zu diesem Zweck müssen Mikrocontroller Signale empfangen und/oder senden. Mit anderen Worten: Die Beispielprogramme alleine reichen zum Ausprobieren nicht aus. Deshalb wird zu Beginn des Kapitels 5 eine AVR-Experimentierplatine beschrieben. Diese ist in der Lage, AVR-Mikrocontroller im PDIP-20-Gehäuse aufzunehmen. Alle in diesem Buch beschriebenen Anwendungen lassen sich mit der AVR-Experimentierplatine und ein paar anwendungsspezifischen Bauteilen realisieren.

## 2 Die AVR-Mikrocontroller-Familie

In diesem Kapitel wird die AVR-Mikrocontroller-Familie besprochen. Nach Auflistung aller z. Z. verfügbaren AVR-Mikrocontroller-Typen und deren Eigenschaften, wird eine Einführung in die AVR-Architektur gegeben. Anschließend werden die Adressierungsarten und kurz die Peripherie der unterschiedlichen AVR-Typen besprochen. Abgeschlossen wird Kapitel 2 mit einer ausführlichen Darstellung des kompletten Befehlssatzes. Die Datenblätter aller in diesem Kapitel beschriebener AVR-Mikrocontroller-Typen befinden sich als PDF-Dateien im Verzeichnis \Data auf der beiliegenden CD (siehe Anhang A.1).

### 2.1 Eigenschaften und Typen

Die wesentlichen Eigenschaften der AVR-Mikrocontroller-Familie sind:

- 89 Ein-Wort Befehle (AT90S1200) bzw. 118 bis 121 Ein-Wort Befehle

- Fast alle Befehle benötigen nur einen Maschinenzyklus (z. B. 125 ns bei 8 MHz)

- Taktfrequenz von DC bis maximal 12 MHz

- 16-Bit breite Befehle

- 8-Bit breiter Datenbus

- 512 Worte bis 64 kWorte internes FLASH für Programme

- 32 General Purpose Register (GPR)

- 3-Level Hardware Stack (AT90S1200) bzw. Stackpointer im SRAM

- Direkte-, Indirekte- und Relative-Adressierung

- Interner Analog-Komparator

- 8-Bit Timer/Counter mit programmierbaren 10-Bit Verteiler

- 16-Bit Timer/Counter mit Capture Compare Mode

- 1 bis 3 PWM-Kanäle

- 10-Bit Analog/Digital-Wandler mit 8 Kanäle

- 5 bis 48 I/O-Leitungen

- Watchdog Timer mit chipinternen RC-Oszillator

- Programmierbare Sicherung gegen auslesen des Programm-codes

Die einzelnen Familienmitglieder und deren Eigenschaften faßt Tabelle 2.1 zusammen.

Ganz grob kann man die einzelnen Typen in folgende Kategorien unterteilen: Der AT90S1200 ist das kleinste Mitglied der Familie. Er verfügt im Gegensatz zu allen übrigen AVR-Typen über einen Hardware-Stack und kein internes SRAM (Statisches Random Access Memory). Ferner kann der AT90S1200 den Speicher nur direkt adressieren. Der AT90S2313 hingegen ist eine deutliche Erweiterung zum AT90S1200. Er verfügt im Vergleich zum AT90S1200 über den doppelten Programm- und EEPROM-Speicher (Electrically Erasable and Programmable Read Only Memory) sowie über 128 Bytes SRAM, einen UART (Universal Asynchronous Receiver and Transmitter), einem 16-Bit Timer/Counter und einem PWM-Kanal (Pulse Width Modulator). Die Typen AT90S2323 und AT90S2343 sind in einem 8-poligen Gehäuse untergebracht. Sie sind ansonsten, abgesehen von der Peripherie, mit dem AT90S2313 vergleichbar. Die nächste Kategorie bilden die beiden Typen AT90S4414 und AT90S8515. Beide sind bis auf die Größe der Speicher identisch. Analoges gilt für die

|                          | AT90S1200          | AT90S2313          | AT90S2323          | AT90S2343          | AT90S4414          | AT90S4414          | AT90S8515          | AT90S8515          | ATmega103   | ATmega163  |

|--------------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|-------------|------------|

| Betriebe                 | 89                 | 120                | 120                | 120                | 120                | 120                | 118                | 120                | 118         | 121        |

| Programmspeicher         | 1-K Byte           | 2-K Bytes          | 2-K Bytes          | 2-K Bytes          | 4-K Bytes          | 4-K Bytes          | 8-K Bytes          | 8-K Bytes          | 128 K Bytes | 64 K Bytes |

| EEPROM                   | 64 Bytes           | 128 Bytes          | 128 Bytes          | 128 Bytes          | 256 Bytes          | 256 Bytes          | 512 Bytes          | 512 Bytes          | 4 K Bytes   | 2 K Bytes  |

| SRAM                     | -                  | -                  | -                  | -                  | -                  | -                  | -                  | -                  | -           | -          |

| General Purpose Register | 32                 | 32                 | 32                 | 32                 | 32                 | 32                 | 32                 | 32                 | 32          | 32         |

| Stack                    | 10                 | 15                 | 15                 | 5                  | 5                  | 32                 | 32                 | 32                 | 48          | 48         |

| max. Taktfrequenz        | 12 MHz             | 10 MHz             | 8 MHz              | 8 MHz              | 8 MHz              | 8 MHz              | 8 MHz              | 8 MHz              | 6 MHz       | 6 MHz      |

| 8-Bit Timer/Counter      | -                  | -                  | -                  | -                  | -                  | -                  | -                  | -                  | -           | -          |

| 16-Bit Timer/Counter     | -                  | -                  | -                  | -                  | -                  | -                  | -                  | -                  | -           | -          |

| Capture/Compare Mode     | -                  | -                  | -                  | -                  | -                  | -                  | -                  | -                  | -           | -          |

| PWM                      | -                  | -                  | -                  | -                  | -                  | -                  | -                  | -                  | -           | -          |

| Analog-Comparators       | -                  | -                  | -                  | -                  | -                  | -                  | -                  | -                  | -           | -          |

| UART                     | -                  | -                  | -                  | -                  | -                  | -                  | -                  | -                  | -           | -          |

| SPI                      | -                  | -                  | -                  | -                  | -                  | -                  | -                  | -                  | -           | -          |

| 10-Bit ADC               | -                  | -                  | -                  | -                  | -                  | -                  | -                  | -                  | -           | -          |

| RTC                      | -                  | -                  | -                  | -                  | -                  | -                  | -                  | -                  | -           | -          |

| Gehäuse                  | PDP-20,<br>SOIC-20 | PDP-40,<br>SOIC-40 | TQFP-44     | TQFP-44    |

Tabelle 2.1: Die AVR-Mikrocontroller-Familie.

Typen AT90S4434 und AT90S8535. Im Gegensatz zu den Typen AT90S4414 und AT90S8515 besitzen sie einen 10-Bit Analog/Digital-Wandler mit acht Kanälen. Die letzte Kategorie bilden die Typen ATmega103 und ATmega603 mit 64 kWorte bzw. 32 kWorte.

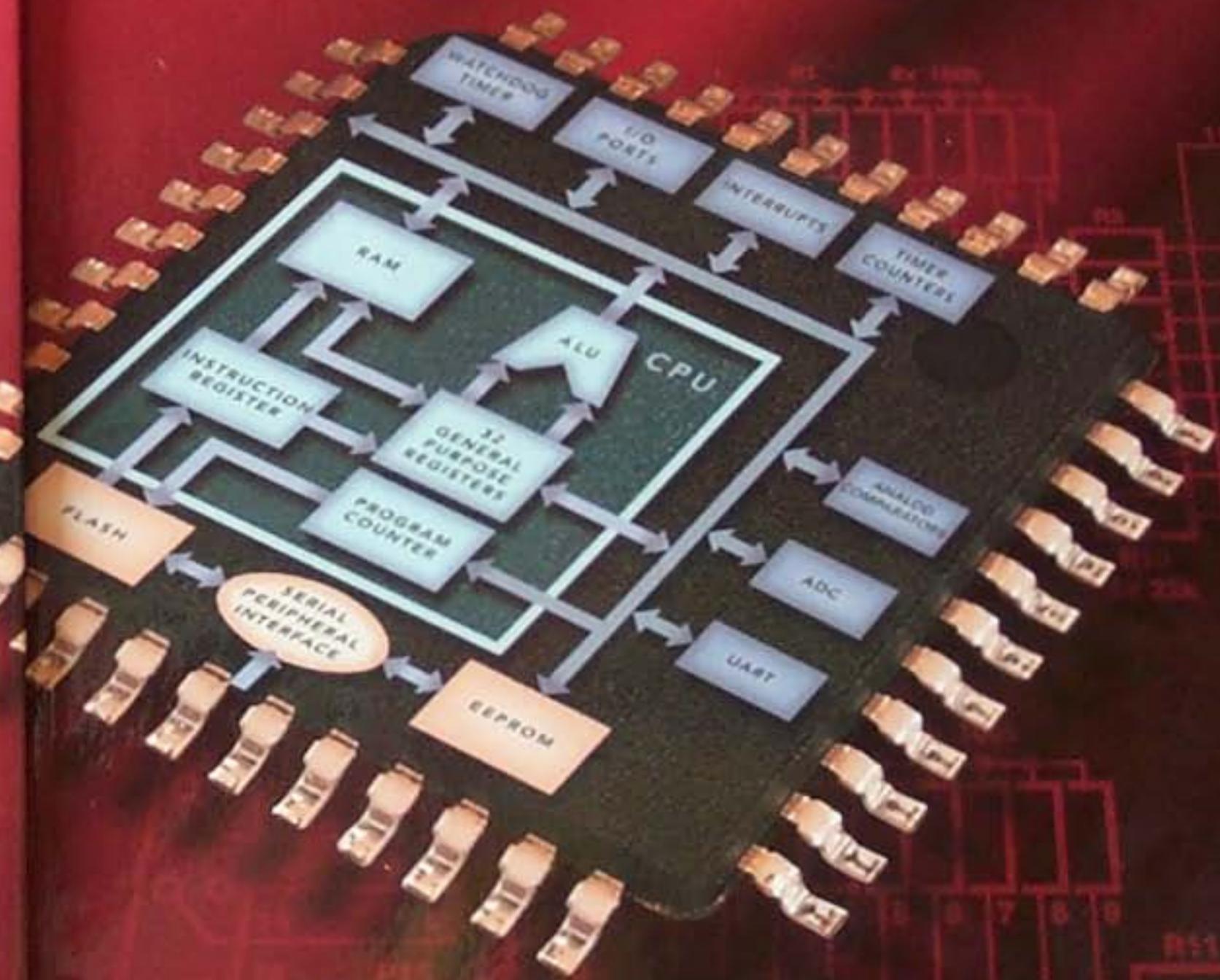

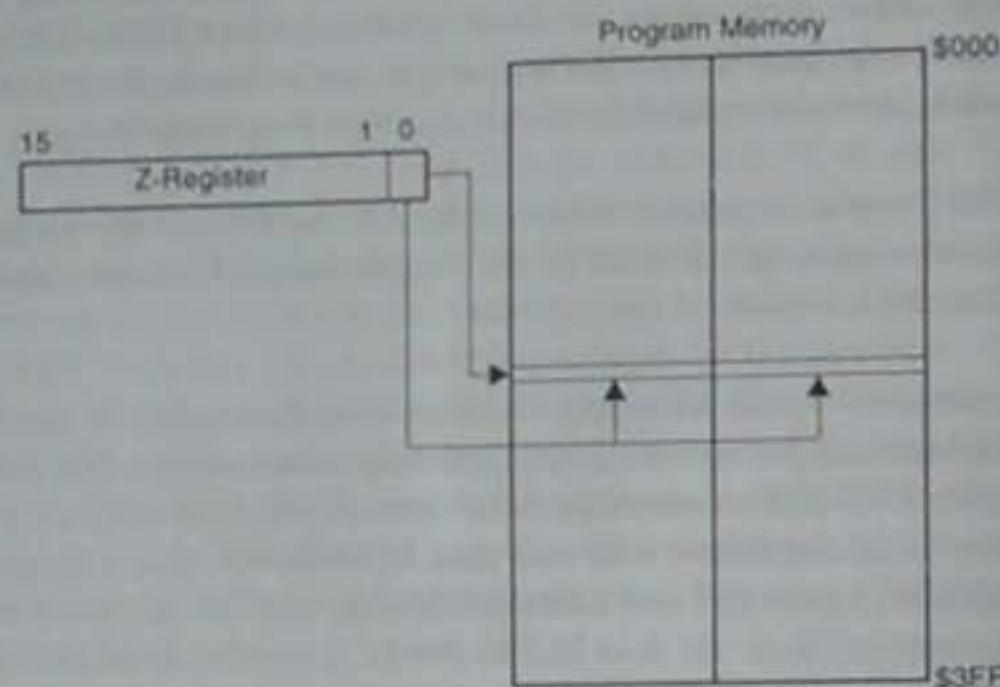

## 2.2 AVR-Architektur

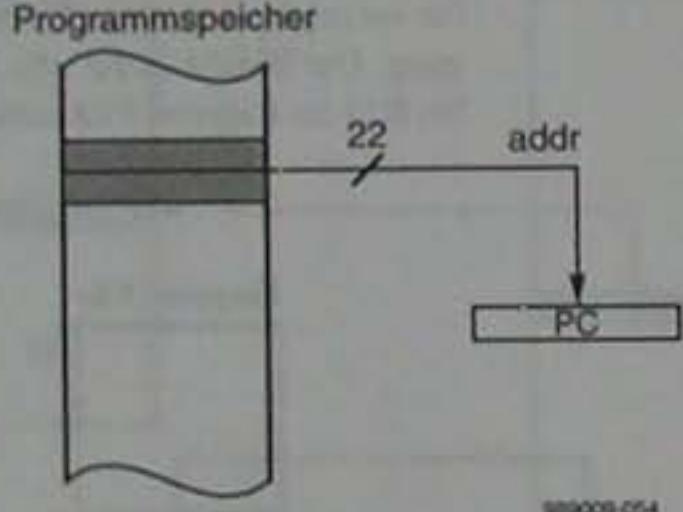

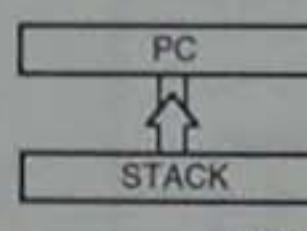

Die AVR-Mikrocontroller Familie weist Merkmale auf, die bei RISC (Reduced Instruction Set Computer) implementiert sind. Abweichend von anderen Controllern, die einen Bus für Befehle und Daten verwenden (von Neumann-Architektur), verwendet die AVR-Familie zwei getrennte Busse und Speicher für Befehle und Daten (Harvard-Architektur). Dadurch ist es möglich, verschieden breite Busse für Daten und Befehle zu benutzen. Die AVRs haben einen 8-Bit breiten Bus für Daten und einen 16-Bit breiten Bus für Befehle. Durch den breiteren Bus für die Befehle ist es möglich, fast alle Befehle als Ein-Wort Befehle zu implementieren. Durch die einstufige Pipeline kann, während ein Befehl ausgeführt wird, der nächste bereits aus dem Programmspeicher geholt werden. Der Programmzähler (PC, Program Counter) ist, je nach AVR-Mikrocontroller Typ und damit je nach Programmspeichergröße, zwischen 9- und 16-Bit breit und befindet sich im I/O-Adressbereich (s. u.). Während eines Interrupts oder beim Aufrufen einer Unterprogrammroutine wird der Inhalt des PC auf den Stack abgelegt. Der AT90S1200 verfügt über einen 3-Level Hardware-Stack. Alle anderen AVR-Mikrocontroller Typen legen den Stack im SRAM ab und greifen über einen Stack-Pointer (SP) auf diesen zu. Der Stack-Pointer ist 16-Bit breit und befindet sich ebenfalls im I/O-Adressraum.

Die einzelnen Typen der AVR-Familie unterscheiden sich in der Größe des Programmspeichers, der zwischen  $512 \times 16$  Bit und  $65536 \times 16$  Bit liegt, Größe des EEPROM-Datenspeichers (zwischen 64 Byte und 2 kByte), Größe des internen SRAM-Datenspeichers (zwischen 128 Byte und 4 kByte), der Anzahl der Ports und der implementierten Peripherie, wie Analog/Digital-Wandler, UART usw. Für die Peripherie sind insgesamt 64 I/O-Speicherstellen vor-

geschen, die direkt über den OUT-Befehl angesprochen werden können. Alternative lassen sich diese I/O-Speicherstellen im Adressraum \$20 bis \$5F des Datenspeichers ansprechen.

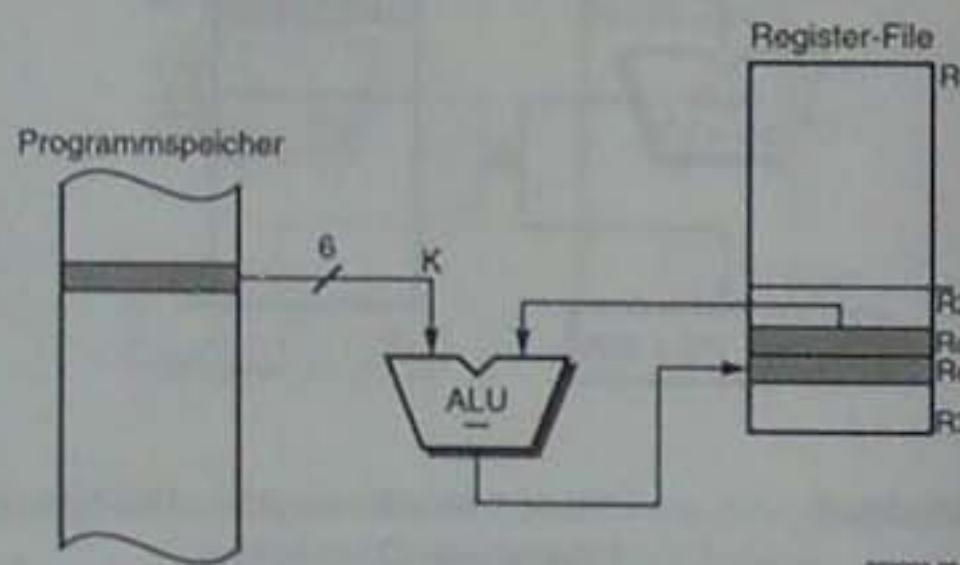

Bild 2.1: Architektur der AVR-Mikrocontroller Familie.

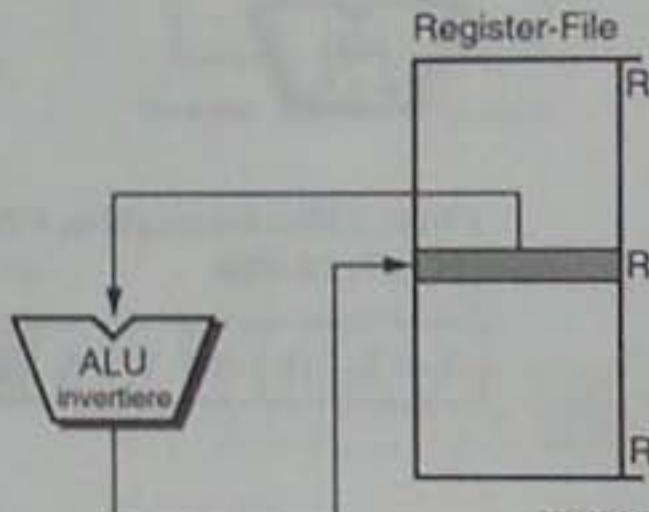

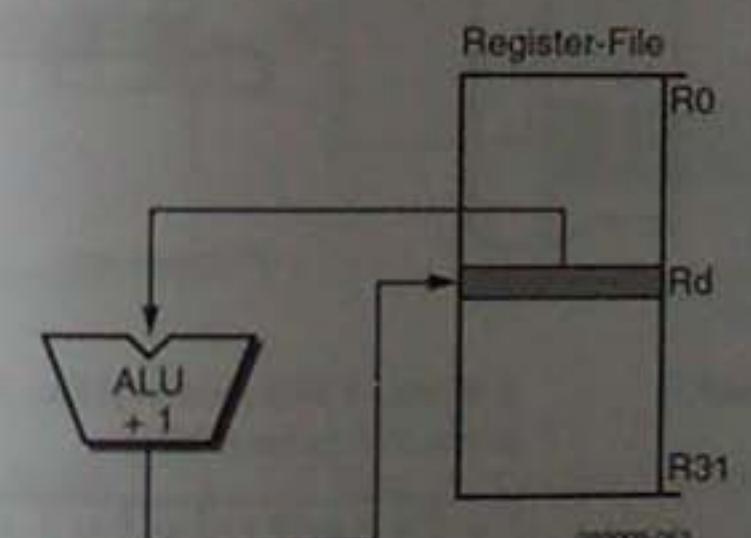

Der Controllerkern verfügt über eine 8-Bit breite ALU (Arithmetic Logic Unit), die zusammen mit den 32 Allzweckregister (GPR, General Purpose Register R0...R31), im folgenden einfach nur Register genannt, direkt verbunden ist. Diese 32 Register sind ungefähr das, was bei anderen Mikrocontrollern der Akkumulator ist. Alle 32 Register sind im Adreßraum des Datenspeichers gemappt (dazu später mehr). Beim AT90S1200 dient das letzte Register, bei den anderen Familienmitgliedern die letzten drei Register als Pointer (Zeiger). Die ALU ist in der Lage, Addition, Subtraktion, Shift (Bit schieben) und logische Operationen durchzuführen. So kann man beispielsweise eine Addition zwischen den Registern R1 und R2 und das anschließende Zurückspeichern des Ergebnisses in eines der beiden Register in einem Befehl mit einem Zyklus ausführen. Abhängig vom Ausgang der Verknüpfung setzt die ALU Flags im STATUS-Register (SREG).

Der Zugriff auf den Datenspeicherbereich (also auch auf die Register) kann mit insgesamt fünf Adressierungsarten erfolgen (siehe Abschnitt 2.3).

## 2.3 Speicher und Register

### 2.3.1 Programmspeicher

Der Programmspeicher bei der AVR-Mikrocontroller Familie ist als Flash ausgeführt und ist 16-Bit breit. Flash-Speicher bietet den Vorteil, daß sie elektrisch programmier- und auch elektrisch wieder lösbar sind. Der Programmspeicher ist mindestens 1000 mal lösch- und programmierbar.

Der Programmspeicher läßt sich bei den AVR-Mikrocontrollern auf zwei unterschiedliche Arten programmieren: Zum einen parallel, d. h. die zu programmierenden Daten werden parallel mit je 8 Bit an die Anschlüsse PB0 bis PB7 angelegt (siehe Datenblätter). Es besteht aber auch die Möglichkeit, den Programmspeicher seriell über eine SPI-Schnittstelle (Serial Peripheral Interface) zu programmieren. Da-

mit ist es sogar möglich, die Mikrocontroller in der Schaltung (In-Circuit) zu programmieren. Dazu werden die Anschlüsse PB5 bis PB7 verwendet. Der AVR-Programmer, der in Kapitel 4 vorgestellt wird, verwendet ausschließlich die serielle Programmierung.

Der Programmspeicher wird von der Adresse 0 linear bis zur Endadresse adressiert. Die Größe des Programmspeicher kann man aus Tabelle 2.1 (Seite 11) entnehmen.

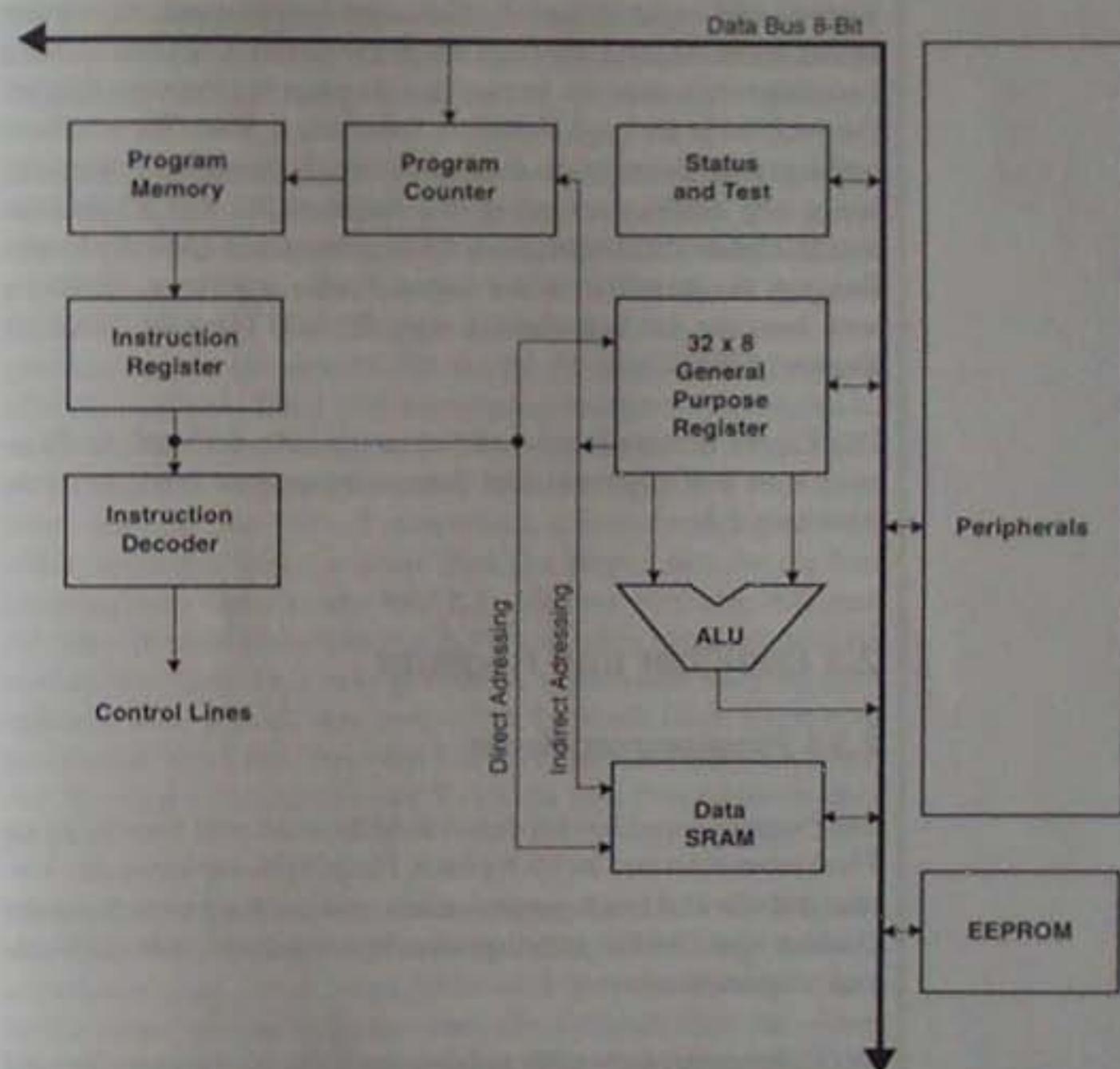

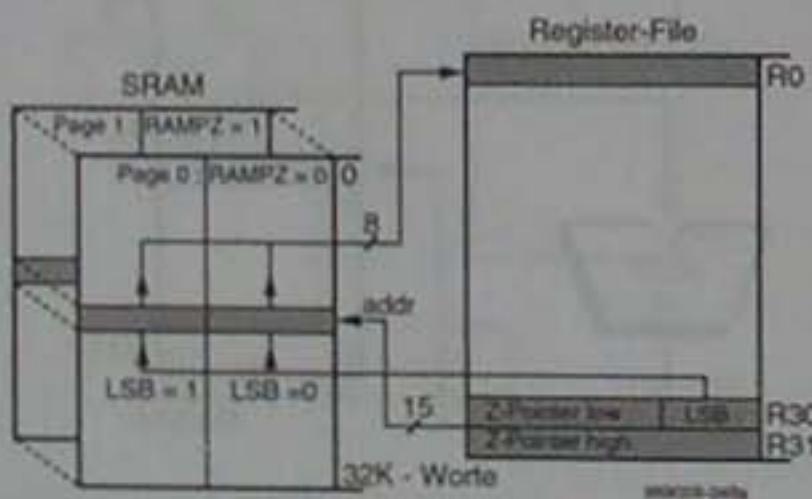

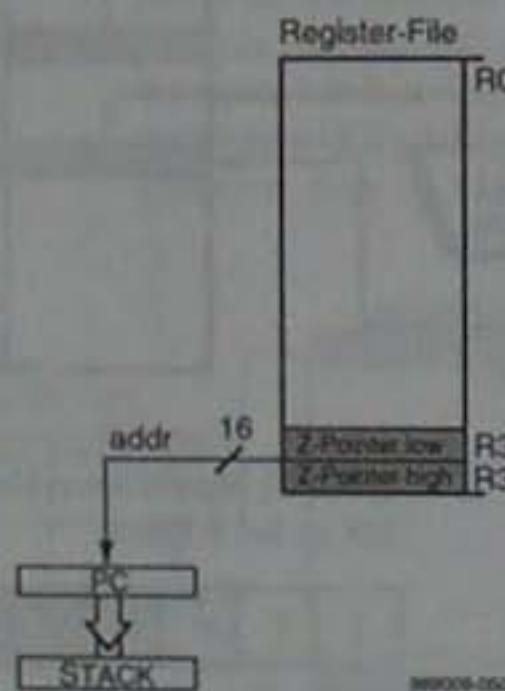

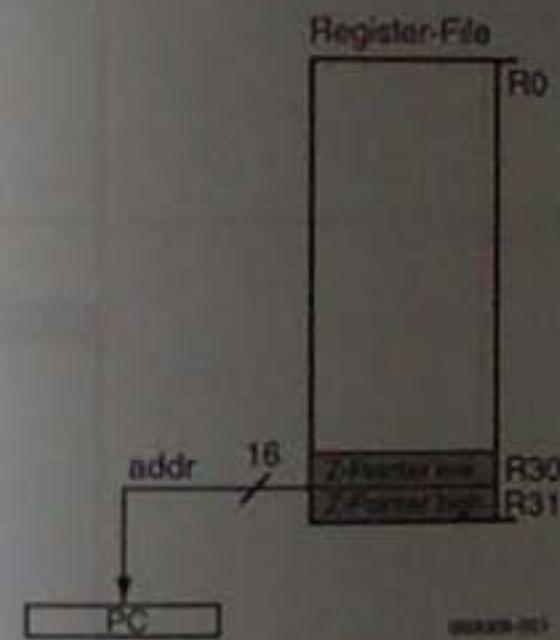

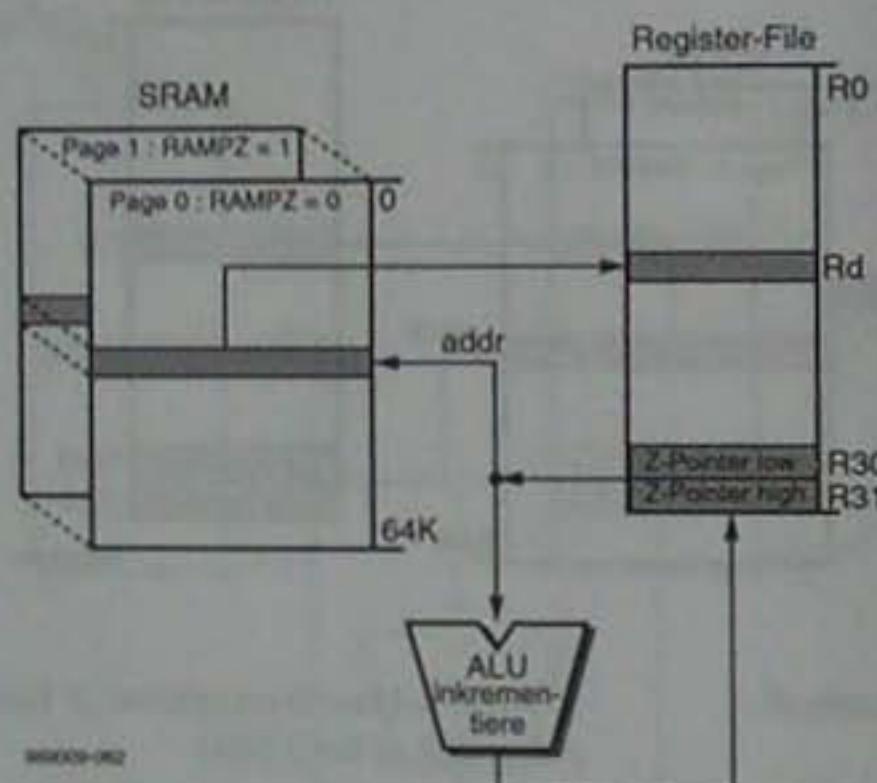

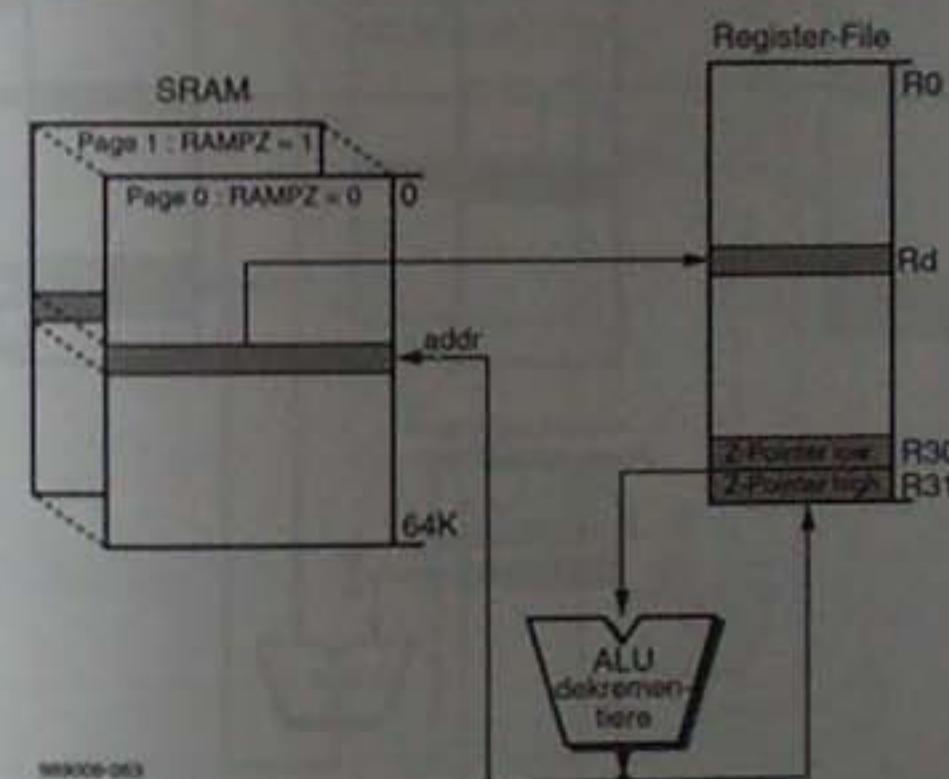

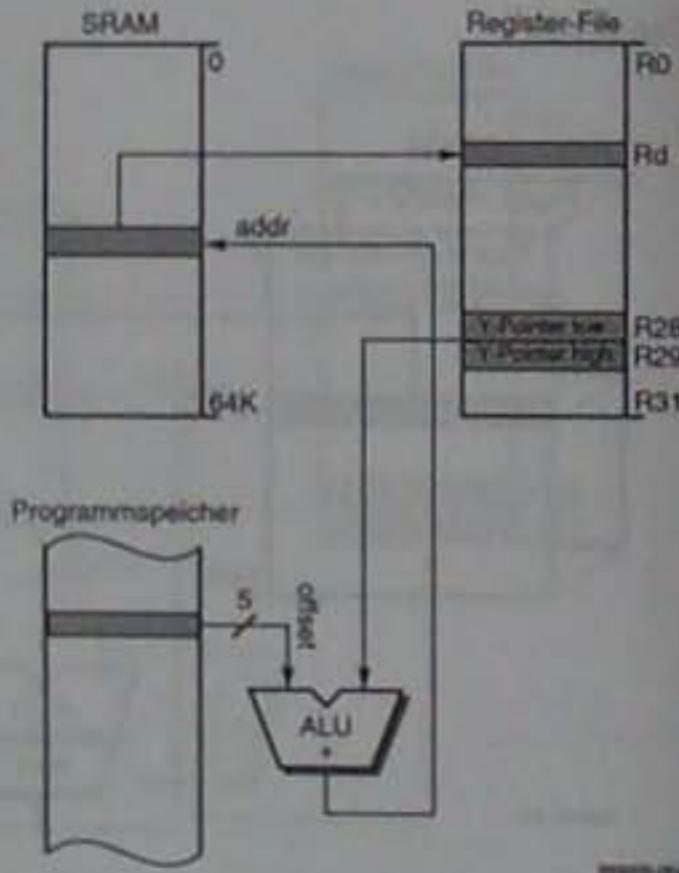

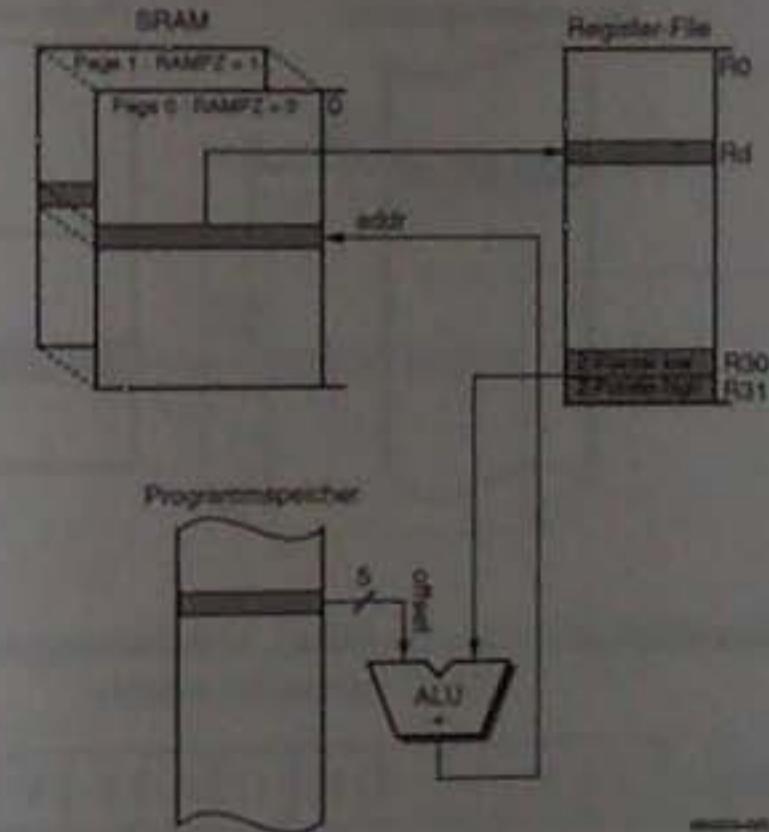

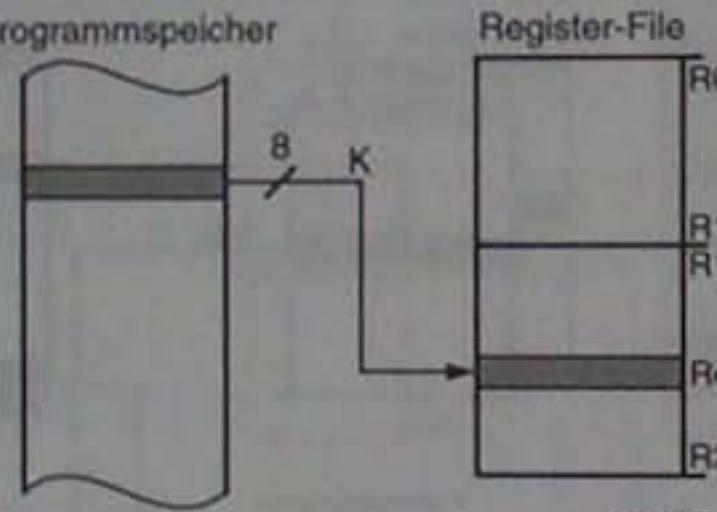

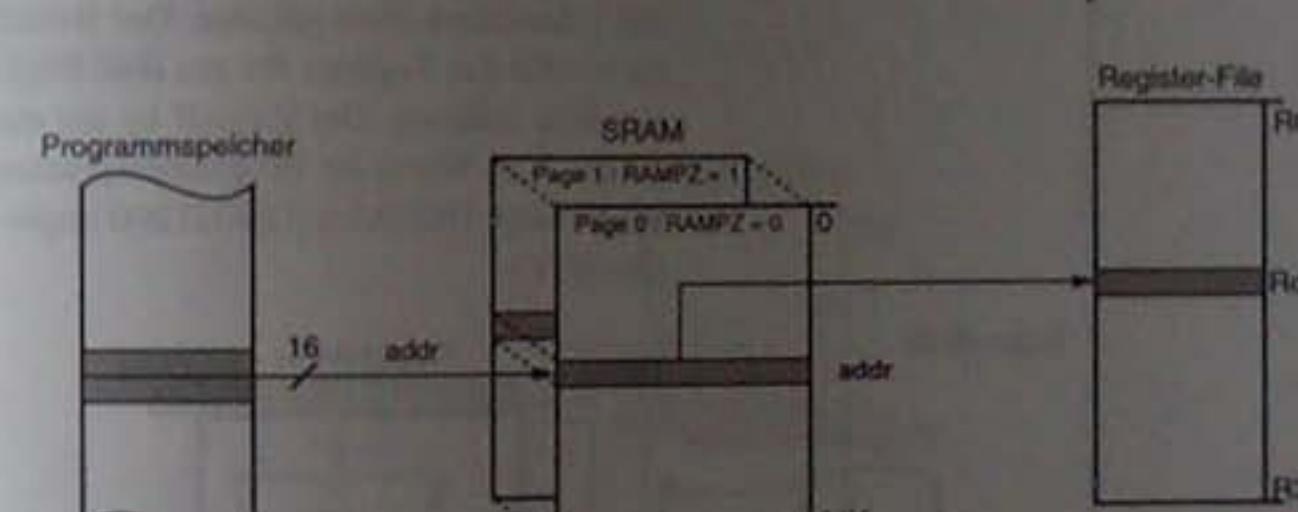

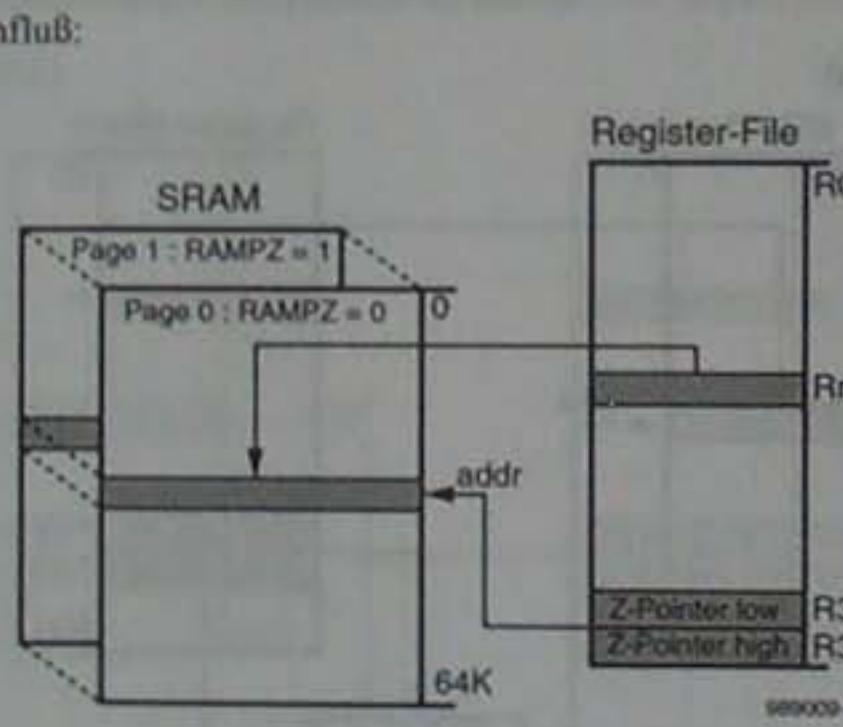

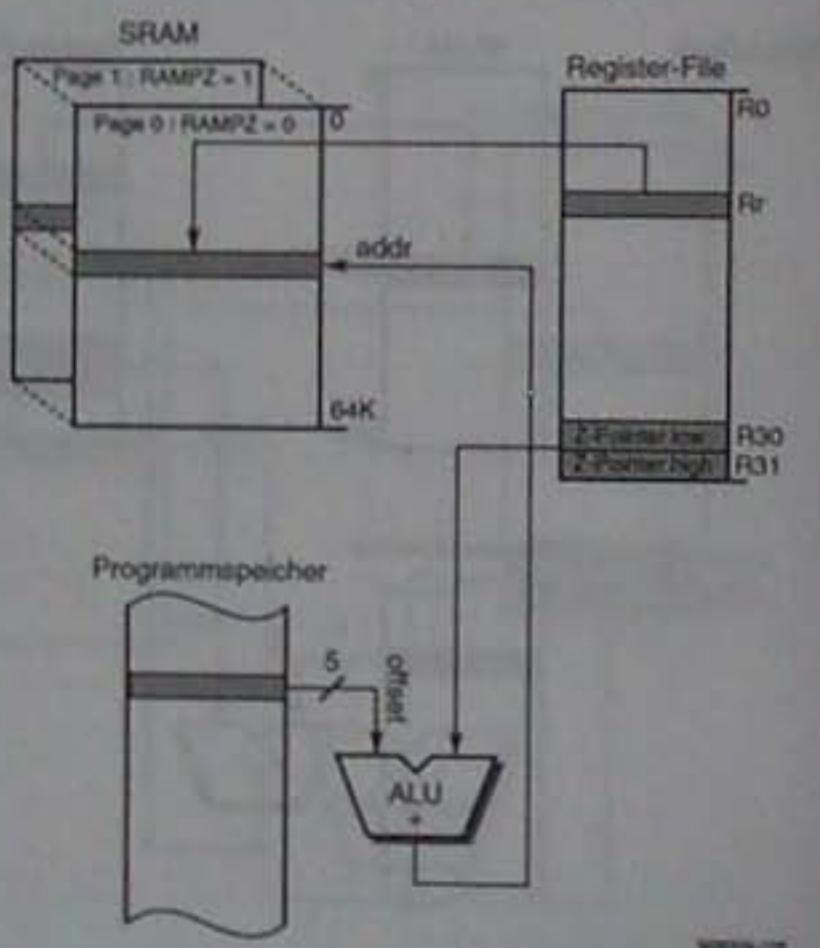

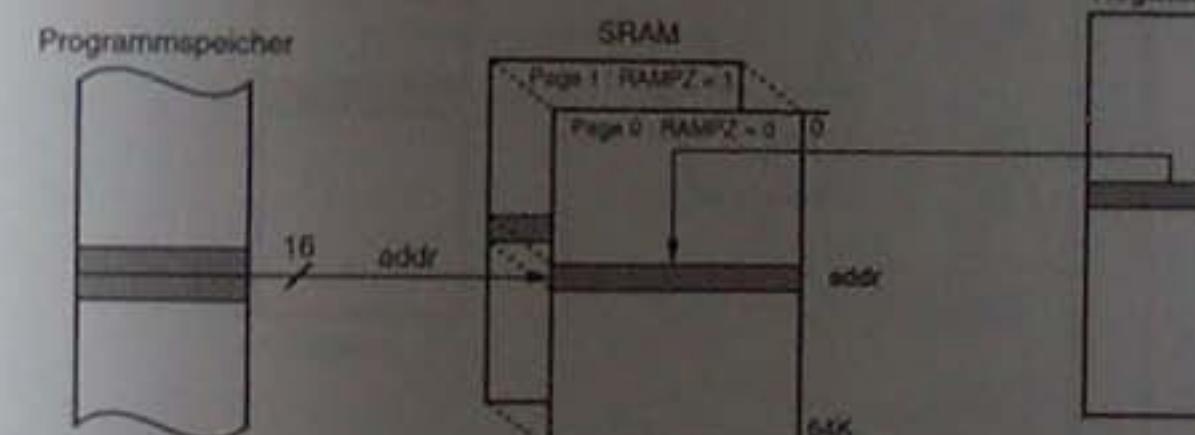

Interessant ist die Möglichkeit, Daten bzw. Konstanten in eine Tabelle abzulegen, die sich im Programmspeicher befindet. Das ist bei allen AVR-Mikrocontrollern außer beim AT90S1200 möglich. Das Auslesen der Daten wird mit dem LPM-Befehl (Load Program Memory) bzw. bei den ATmega103 aufgrund des größeren Programmspeichers mit dem ELPM-Befehl (Extended Load Program Memory) realisiert. Dazu geht man folgendermaßen vor: Die Adresse, an der die Daten im Programmspeicher stehen, muß in den Z-Pointer (R30 und R31) geladen werden. Man muß beachten, daß diese Adresse in den Bits 1 bis 15 stehen muß. Das niederwertigste Bit 0 wählt das untere bzw. das obere Byte des Wortes aus, das im Programmspeicher steht (siehe Bild 2.2). Hieraus wird klar, daß man die Adresse nicht einfach in den Z-Pointer laden kann, sondern sie erst um eine Stelle nach links geschoben werden oder mit zwei multipliziert werden muß, was zum selben Ergebnis führt. Führt man anschließend den LPM- bzw. den ELPM-Befehl aus, wird das Register R0 mit dem so adressierten Bytes aus dem Programmspeicher geladen.

Mit dem LPM-Befehl lassen sich somit insgesamt 32 kWorte adressieren, da der Z-Pointer in diesem Fall eine 15-Bit lange Adresse aufnehmen kann. Beim ATmega103 wird über den Z-Pointer eine 16-Bit lange Adresse aufgenommen. Die Auswahl über das untere oder obere Byte aus dem Programmspeicher wird über das Bit 0 im RAMPZ-Register (Adresse \$3B im I/O- bzw. \$5B im Datenspeicheradreßraum) vorgenommen. Beide Befehle werden in Abschnitt 2.9 ausführlich erklärt. In den Abschnitten 5.3 und 5.7 sind zwei Beispiele angegeben, bei denen der LPM-Befehl verwendet wird.

**Bild 2.2:**

Laden eines Bytes aus dem Programm-

speicher (hier 1 kWort groß).

### 2.3.2 Datenspeicher (SRAM)

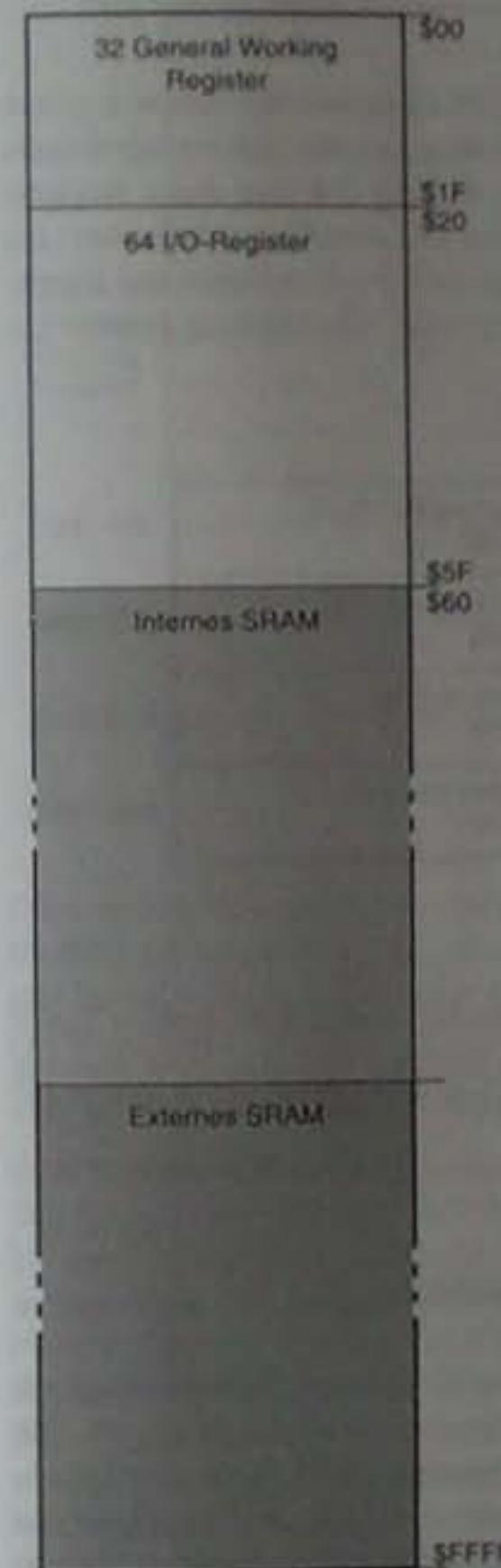

Die AVR-Mikrocontroller verfügen über ein 128 Bytes bis 4 kBytes großes SRAM. Einzige Ausnahme bildet der AT90S1200, der über kein SRAM verfügt (siehe Tabelle 2.1). Dieses SRAM kann z. B. als Datenspeicher dienen. Es wird auch dazu verwendet, den Stack aufzunehmen (siehe Abschnitt 2.6). Die Adreßräume des Programm- und Datenspeichers sind, wie bereits erwähnt, getrennt. Der Adreßraum des Datenspeichers beginnt bei der Adresse 0 und endet bei der Adresse \$FFFF (hexadezimal). Er umfasst also 65536 Speicherstellen (siehe Bild 2.3).

Das SRAM selber beginnt aber erst ab der Adresse \$60. Obwohl die Register R0 bis R31 und die 64 I/O-Speicherstellen direkt ansprechbar sind, die I/O-Speicherstellen z. B. über die Befehle IN und OUT, werden diese in den Datenspeicheradreßraum gespiegelt. Damit ist es möglich, die Register und die I/O-Speicherstellen wie ganz nor-

malen Datenspeicher zu behandeln. Die Register R0 bis R31 befinden sich an den Adressen \$0 bis \$1F und die I/O-Speicherstellen an den Adressen \$20 bis \$5F im Adreßraum des Datenspeichers. Das interne SRAM schließt sich dann ab der Adresse \$60 an. Die Größe des SRAM ist vom AVR-Mikrocontroller abhängig und kann aus der Tabelle 2.1 entnommen werden.

Die Typen AT90S4414 und AT90S8515 sowie die Bausteine ATmega103/603 können zusätzlich externes SRAM ansprechen. Dieser externe Speicher kann nach der letzten Adresse des internen SRAM angeschlossen werden. Da die maximale Größe des internen SRAM 4 kBytes ist (siehe Tabelle 2.1) und der Adreßraum des Datenspeichers maximal 64 kBytes ist, können maximal 60 kBytes externer Datenspeicher adressiert werden.

### 2.3.3 EEPROM

Alle AVR-Mikrocontroller verfügen über ein internes EEPROM. Die Größe dieses EEPROMs kann man wieder der Tabelle 2.1 entnehmen.

**Bild 2.3:**

Der Adreßraum

des Datenspei-

chers

Das EEPROM befindet sich in einem von Programm- und Daten- speicher getrennten Adreßraum.

Das byteweise Schreiben in das EEPROM sowie das Lesen aus dem EEPROM geschieht über spezielle Register, die sich im Adreßraum der I/O-Speicherstellen befinden. In **Bild 2.4** sind diese Register abgebildet. Neben den Adressen im I/O-Adreßraum befinden sich in Klammern die äquivalenten Adressen im Adreßraum des Datenspeichers. Es sei daran erinnert, daß die I/O-Adressen dorthin gespiegelt werden.

**Bild 2.4:**

Steuerregister zum byteweisen Schreiben und Lesen des EEPROMs.

|                                        |             |

|----------------------------------------|-------------|

| EEPROM Adress-Register (high)<br>EEARH | \$1F (\$3F) |

| EEPROM Adress-Register (low)<br>EEARL  | \$1E (\$3E) |

| EEPROM Data-Register<br>EEDR           | \$1D (\$3D) |

| EEPROM Control-Register<br>EECR        | \$1C (\$3C) |

Aufgrund der Größe des EEPROMs besitzen nur die beiden Typen ATmega103 und ATmega603 das Register EEARH. Alle anderen Typen kommen mit einem Adressbyte zur Adressierung des EEPROMs aus.

### 2.3.4 General Purpose Register

Die AVR-Mikrocontroller besitzen 32 General Purpose Register (GPR), im folgenden einfach als Register bezeichnet (**Bild 2.5**). Alle 32 Register sind mit der ALU verbunden. Dadurch ist es möglich, daß alle registerorientierten Befehle einen direkten Zugriff auf die Register besitzen und innerhalb eines einzigen Maschinenzyklus ausgeführt werden. Die Register können auch über den Adreßraum des

| General Purpose Working Register | 7   | 0    | Addr.                |

|----------------------------------|-----|------|----------------------|

|                                  | R0  | \$00 |                      |

|                                  | R1  | \$01 |                      |

|                                  | R2  | \$02 |                      |

|                                  | ... |      |                      |

|                                  | R13 | \$0D |                      |

|                                  | R14 | \$0E |                      |

|                                  | R15 | \$0F |                      |

|                                  | R16 | \$10 |                      |

|                                  | R17 | \$11 |                      |

|                                  | ... |      |                      |

|                                  | R26 | \$1A | X-Register low byte  |

|                                  | R27 | \$1B | X-Register high byte |

|                                  | R28 | \$1C | Y-Register low byte  |

|                                  | R29 | \$1D | Y-Register high byte |

|                                  | R30 | \$1E | Z-Register low byte  |

|                                  | R31 | \$1F | Z-Register high byte |

**Bild 2.5:**

General Purpose Register

Datenspeichers angesprochen werden. Die jeweiligen Adressen sind im **Bild 2.5** angegeben (vgl. Abschnitt 2.3.2). Zu beachten ist, daß alle Befehle, die im Operanden ein Register und einen unmittelbaren Wert haben (SBCI, SUBI, CPI, ANDI, ORI und LDI), nur auf die oberen 16 Register R16 bis R31 angewendet werden können.

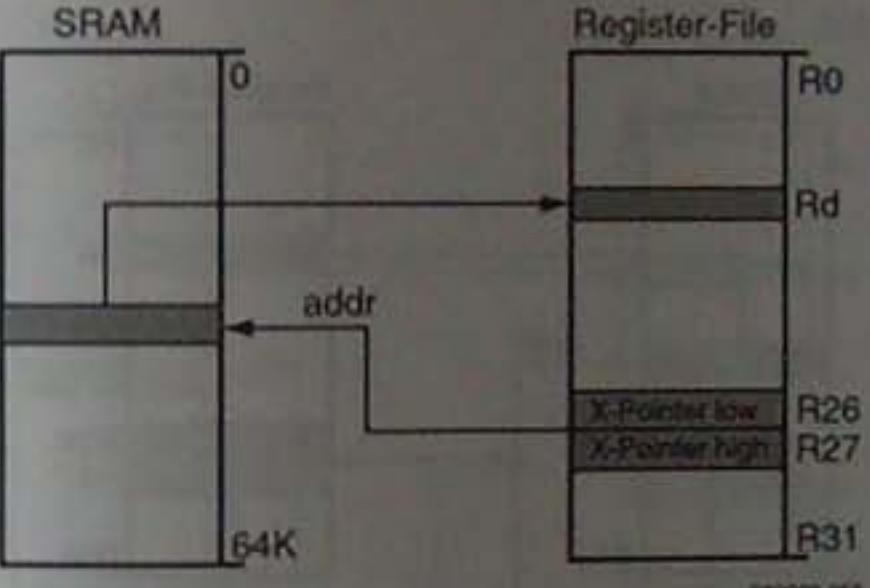

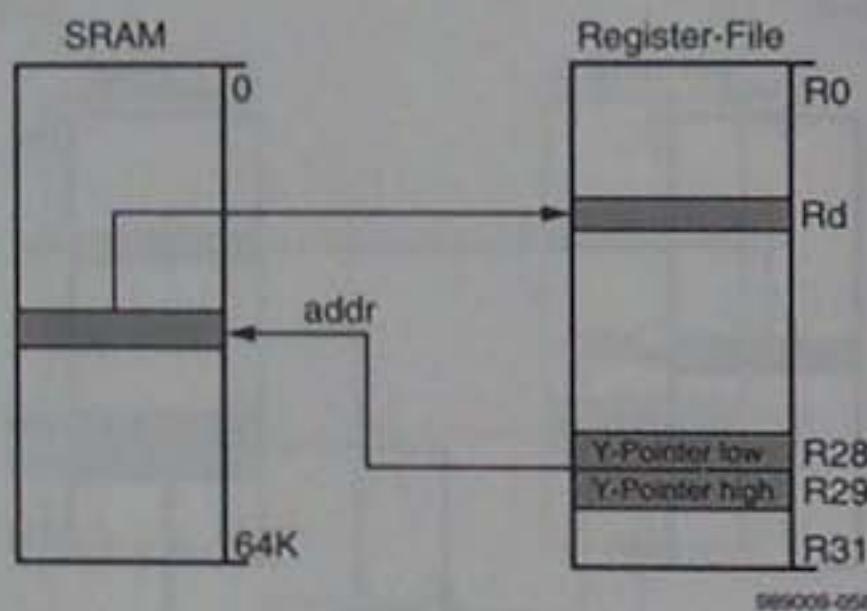

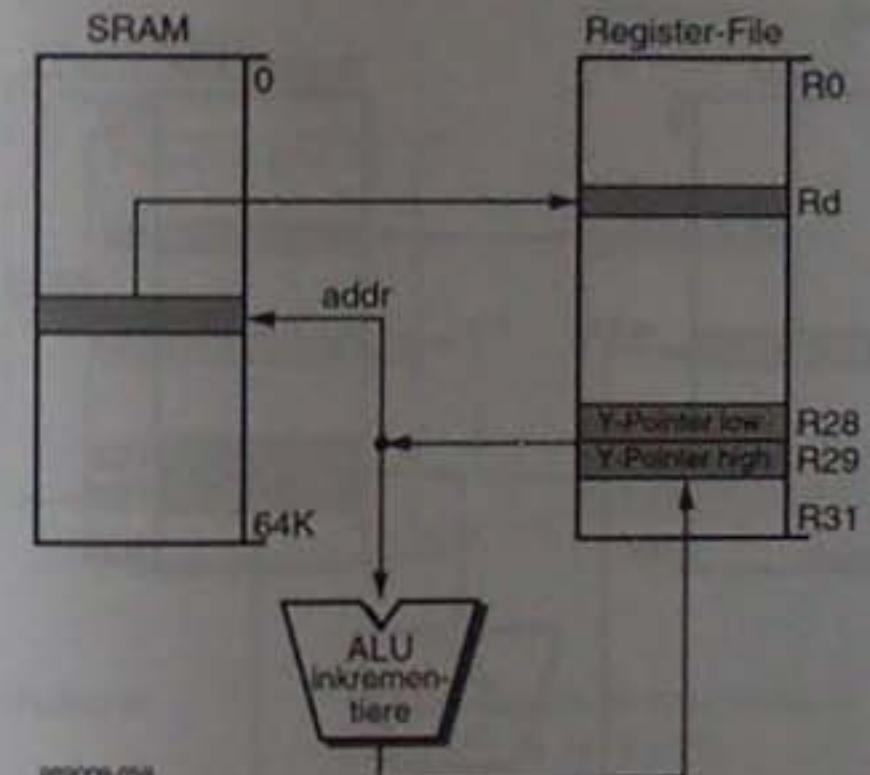

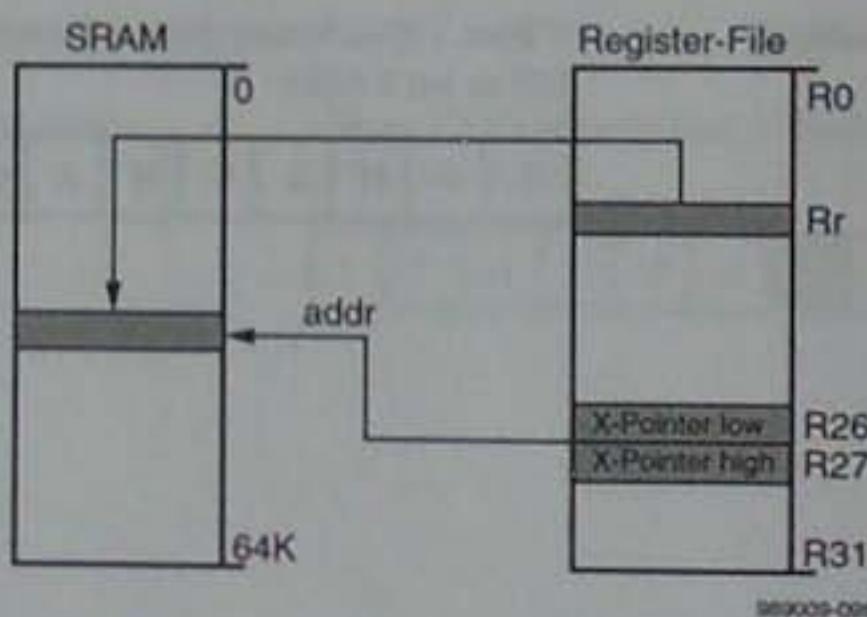

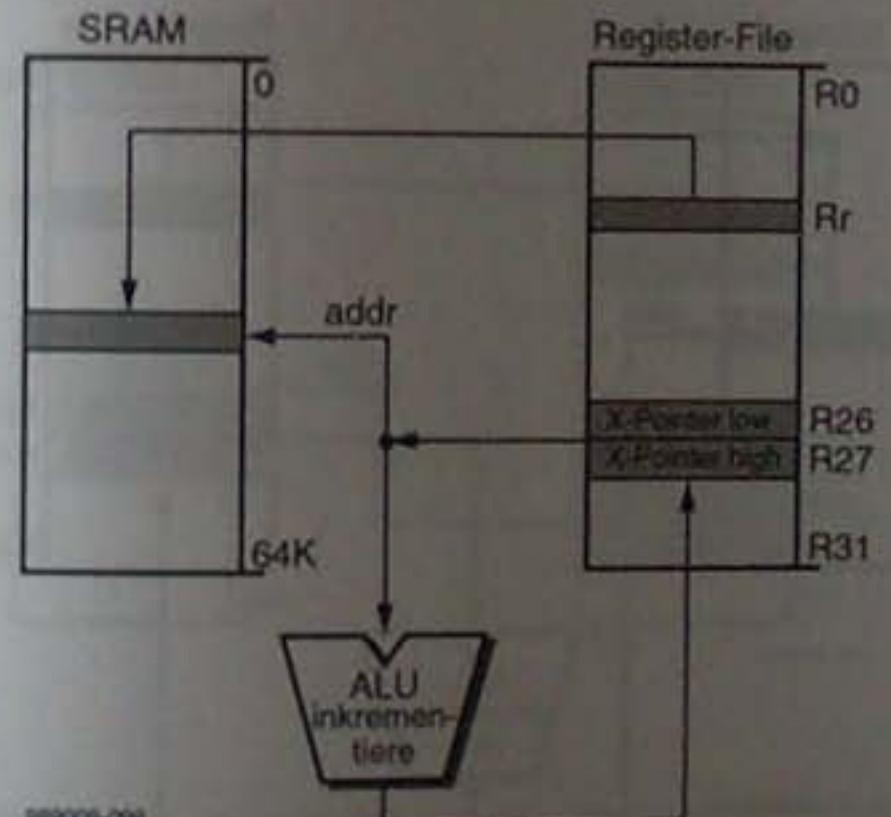

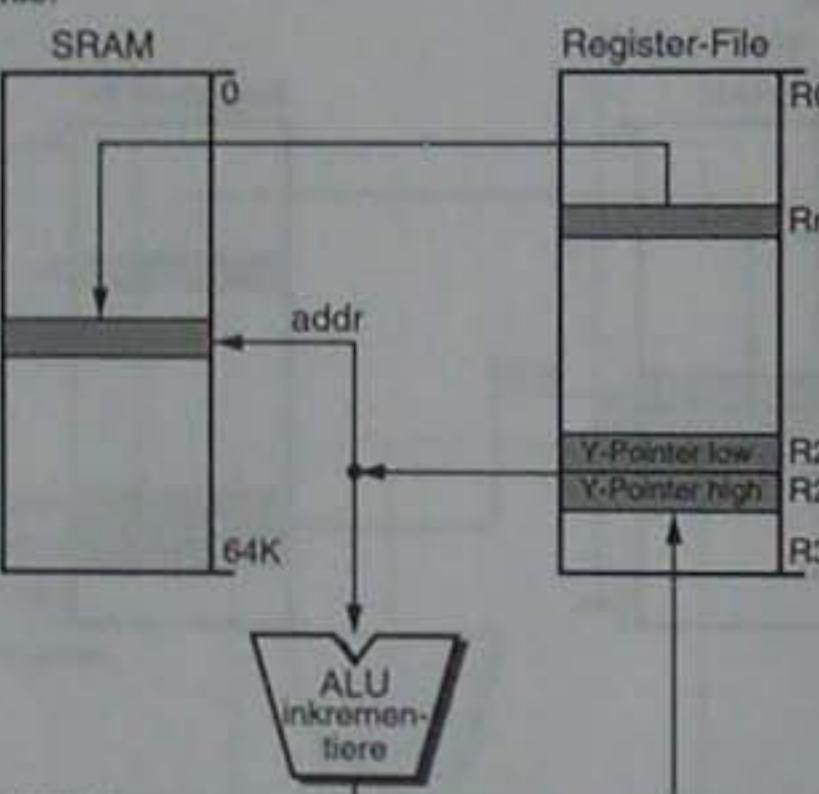

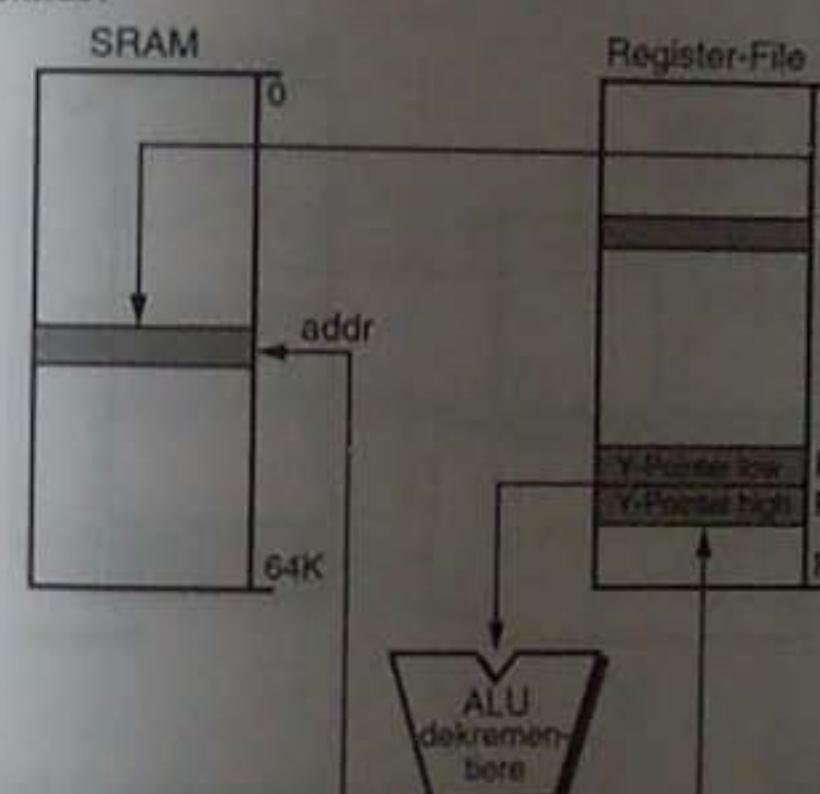

Eine besondere Bedeutung kommt den Registern R26 bis R31 zu. Das Registerpaar R26 und R27 bildet den 16-Bit X-Pointer. Dabei ist das Register R26 das niedrigwertige Byte und R27 das hochwertige Byte. Das Registerpaar R28 und R29 bildet den 16-Bit Y-Pointer. Dabei ist das Register R28 das niedrigwertige Byte und R29 das hochwertige Byte. Schließlich bildet das Registerpaar R30 und R31 den 16-Bit Z-Pointer. Dabei ist das Register R30 das niedrigwertige Byte und R31 das hochwertige Byte. Eine Ausnahme macht wieder der AT90S1200. Bei diesem Mikrocontroller ist nur der Z-Pointer vorhanden. Ferner ist der Z-Pointer nur 8-Bit lang und befindet sich im Register R30.

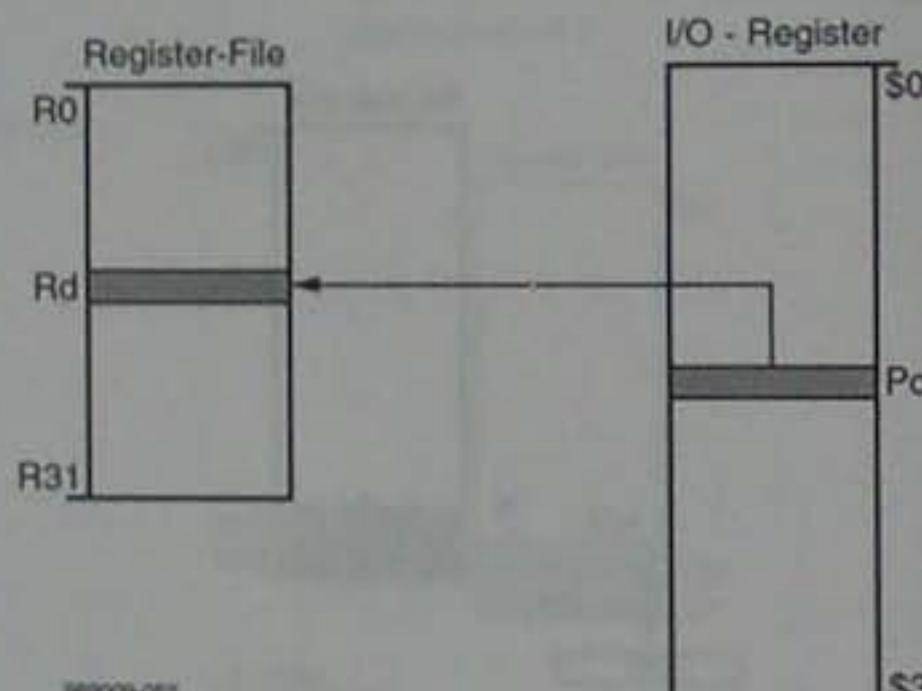

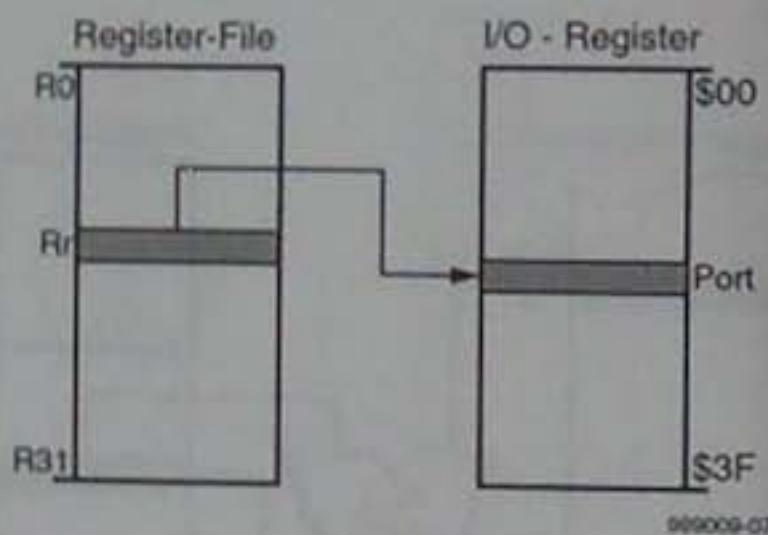

### 2.3.5 I/O-Register

Alle Ports und Peripherie-Module sind im I/O-Adressraum von \$00 bis \$3F der AVR-Mikrocontroller abgelegt. Es handelt sich also um insgesamt 64 I/O-Register. Die I/O-Register sind zum einen über die speziellen Befehle IN und OUT, die Daten zwischen den I/O-Registern und den 32 General Purpose Register austauschen, in dem I/O-Adressraum adressierbar. Zum andern sind die I/O-Register im Adressraum des Datenspeichers gespiegelt (siehe Bild 2.3). Möchte man die I/O-Register wie den Datenspeicher ansprechen, so muß zu den Adressen der I/O-Register \$20 dazu addiert werden.

Über die speziellen I/O-Befehle SBI und CBI (vgl. Abschnitt 2.9) können einzelne Bits in den I/O-Registern gesetzt bzw. gelöscht werden. Es ist aber zu beachten, daß diese zwei Befehle nur auf I/O-Register an den Adressen zwischen \$00 und \$1F angewendet werden können.

Nicht alle AVR-Mikrocontroller haben an allen 64 I/O-Adressen auch physikalisch ein Register implementiert. Aufgrund der implementierten Peripherie sind mehr oder weniger I/O-Register notwendig. Das Datenblatt des jeweiligen AVR-Mikrocontroller-Typs gibt Aufschluß darüber, welche I/O-Adressen mit I/O-Registern belegt sind (siehe Verzeichnis \Data auf der beiliegenden CD). In Tabelle 2.2 sind alle I/O-Register aufgelistet. Die beiden AVR-Mikrocontroller ATmega103/603 besitzen für die I/O-Register teilweise andere Adressen, die Abweichungen sind in der Tabelle in der letzten Spalte aufgeführt.

Tabelle 2.2:

I/O-Register.

| I/O-Adresse | Register   | Funktion                        | Abweichung bei ATmega103/603                                                 |

|-------------|------------|---------------------------------|------------------------------------------------------------------------------|

| \$3F        | SREG       | Status Register                 |                                                                              |

| \$3E        | SPH        | Stack Pointer High              |                                                                              |

| \$3D        | SPL        | Stack Pointer Low               |                                                                              |

| \$3C        | reserviert |                                 |                                                                              |

| \$3B        | GIMSK      | General Interrupt Mask Register | XDIV XTAL Divide Control Register                                            |

| \$3A        | GPIO       | General Interrupt Flag Register | RAMPZ RAM Page 2 Select Register<br>EICR External Interrupt Control register |

|      |            |                                                    |                                             |

|------|------------|----------------------------------------------------|---------------------------------------------|

| \$39 | TIMSK      | Timer/Counter Interrupt Mask Register              | EDMASK External Interrupt Mask Register     |

| \$38 | TIFR       | Timer/Counter Interrupt Flag Register              | EDIFR External Interrupt Flag Register      |

| \$37 | reserviert | TIMSK                                              |                                             |

| \$36 | reserviert | TIFR                                               |                                             |

| \$35 | MCUCR      | MCU General Control Register                       |                                             |

| \$34 | reserviert | MCUSSR MCU Status Register                         |                                             |

| \$33 | TCCR0      | Timer/Counter0 Control Register                    |                                             |

| \$32 | TCNT0      | Timer/Counter0 (8-Bit)                             |                                             |

| \$31 | reserviert | OCR0 Timer/Counter0 Output Compare Register        |                                             |

| \$30 | reserviert | ASSR Asynchronous Mode Status Register             |                                             |

| \$2F | TCCR1A     | Timer/Counter1 Control Register A                  |                                             |

| \$2E | TCCR1B     | Timer/Counter1 Control Register B                  |                                             |

| \$2D | TCNT1H     | Timer/Counter1 High Byte                           |                                             |

| \$2C | TCNT1L     | Timer/Counter1 Low Byte                            |                                             |

| \$2B | OCRAH      | Timer/Counter1 Output Compare Register A High Byte |                                             |

| \$2A | OCRAL      | Timer/Counter1 Output Compare Register A Low Byte  |                                             |

| \$29 | OCR1BH     | Timer/Counter1 Output Compare Register B High Byte |                                             |

| \$28 | OCR1BL     | Timer/Counter1 Output Compare Register B Low Byte  |                                             |

| \$27 | reserviert | ICRH                                               |                                             |

| \$26 | reserviert | ICRL                                               |                                             |

| \$25 | ICRH       | T/C1 Input Capture register High Byte              | TCCR2 Timer/Counter2 Control Register       |

| \$24 | ICRL       | T/C1 Input Capture register Low Byte               | TCNT2 Timer/Counter2 (8-Bit)                |

| \$23 | reserviert |                                                    | OCR2 Timer/Counter2 Output Compare Register |

| \$22 | reserviert |                                                    |                                             |

| \$21 | WDTCSR     | Watchdog Timer Control Register                    |                                             |

| \$20 | reserviert |                                                    |                                             |

| \$1F | EEARH      | EEPROM Address Register High Byte                  |                                             |

| \$1E | EEARL      | EEPROM Address Register Low Byte                   |                                             |

| \$1D | EEDR       | EEPROM Data Register                               |                                             |

| \$1C | EECR       | EEPROM Control Register                            |                                             |

| \$1B | PORTA      | Data Register Port A                               |                                             |

| \$1A | DDRA       | Data Direction Register Port A                     |                                             |

| \$19 | PINA       | Input Pins Port A                                  |                                             |

| \$18 | PORTB      | Data Register Port B                               |                                             |

| \$17 | DDRB       | Data Direction Register Port B                     |                                             |

| \$16 | PINB       | Input Pins Port B                                  |                                             |

| \$15 | PORTC      | Data Register Port C                               |                                             |

| \$14 | DDRC       | Data Direction Register Port C                     |                                             |

| \$13 | PINC       | Input Pins Port C                                  |                                             |

| \$12 | PORTD      | Data Register Port D                               |                                             |

| \$11 | DDRD       | Data Direction Register Port D                     |                                             |

| \$10 | PIND       | Input Pins Port D                                  |                                             |

| \$0F | SPDR       | SPI I/O Data Register                              |                                             |

| \$0E | SPSR       | SPI Status Register                                |                                             |

| \$0D | SPCR       | SPI Control Register                               |                                             |

| \$0C | UDR        | UART I/O Data Register                             |                                             |

| \$0B | USR        | UART Status Register                               |                                             |

|      |            |                                               |

|------|------------|-----------------------------------------------|

| \$0A | UCR        | UART Control Register                         |

| \$09 | UBRR       | UART Baud Rate Register                       |

| \$08 | ACSR       | Analog Comparator Control and Status Register |

| \$07 | ADMUX      | ADC Multiplexer Select Register               |

| \$06 | ADCSR      | ADC Control and Status Register               |

| \$05 | ADCH       | ADC Data Register High                        |

| \$04 | ADCL       | ADC Data Register Low                         |

| \$03 | reserviert |                                               |

| \$02 | reserviert |                                               |

| \$01 | reserviert |                                               |

| \$00 | reserviert |                                               |

PORTE Data Register Port E

DDRE Data Direction Register Port E

PINE Input Pins Port E

PINF Input Pins Port F

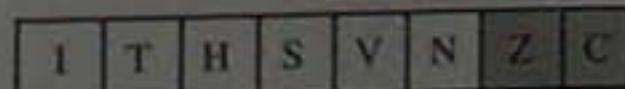

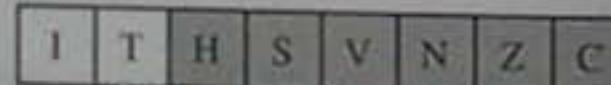

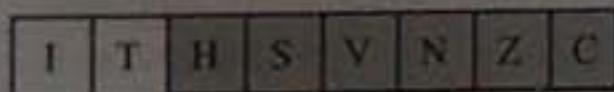

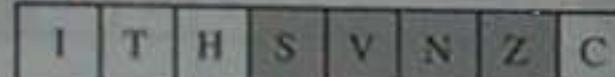

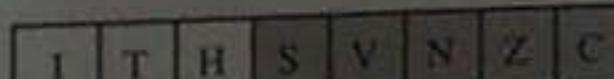

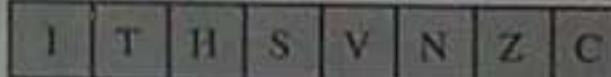

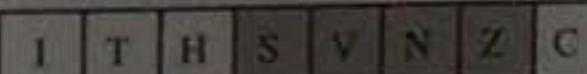

### 2.3.6 STATUS-Register

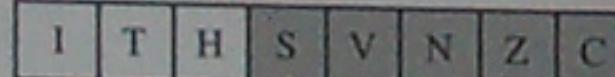

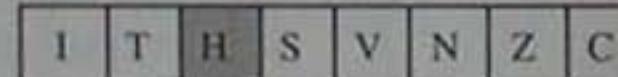

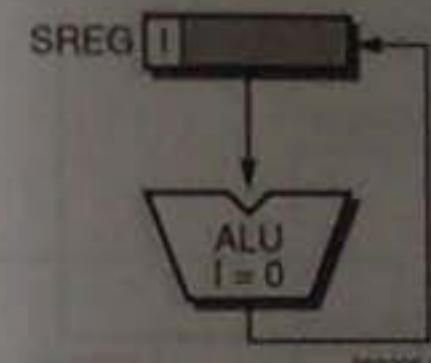

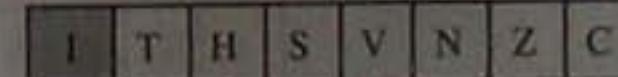

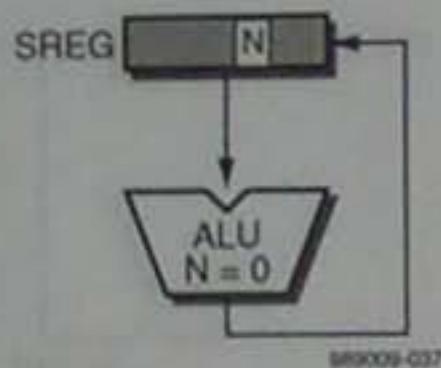

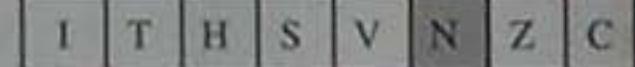

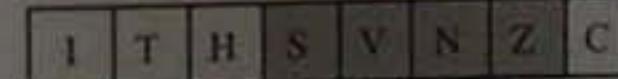

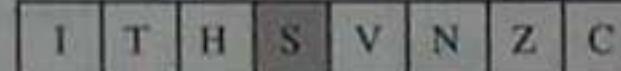

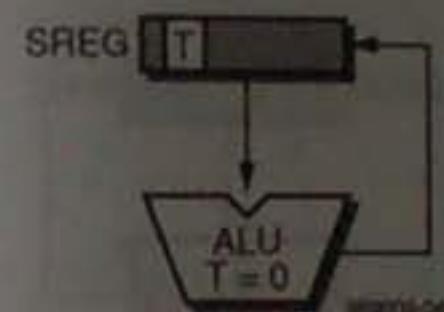

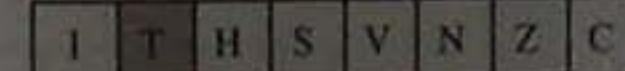

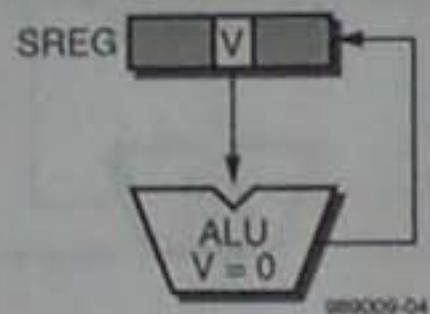

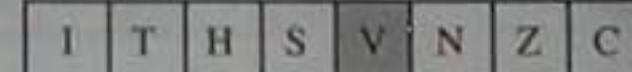

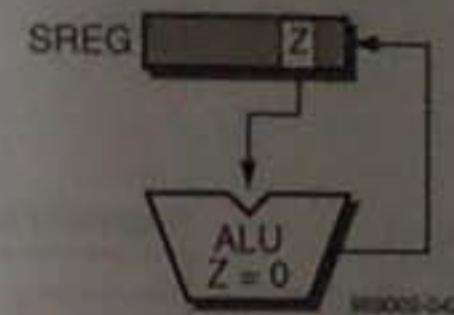

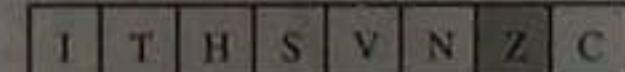

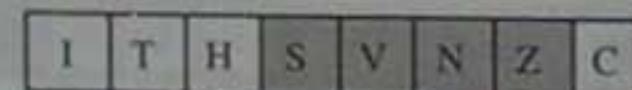

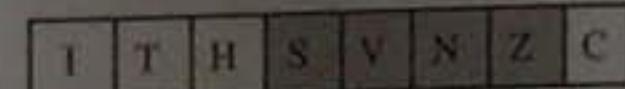

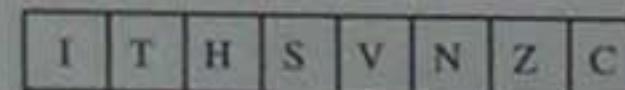

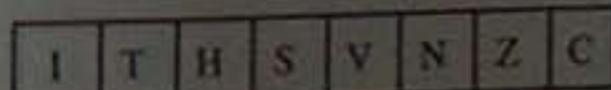

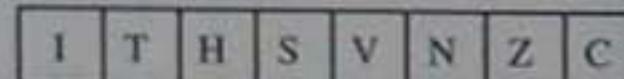

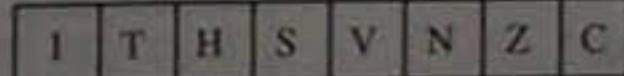

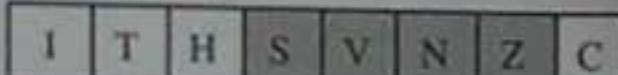

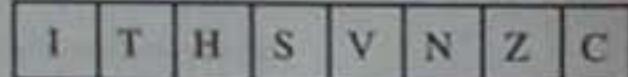

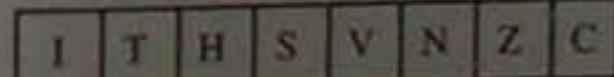

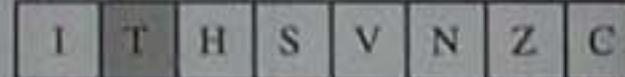

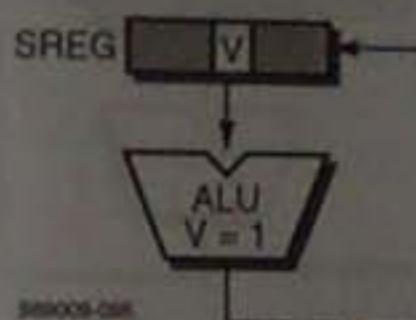

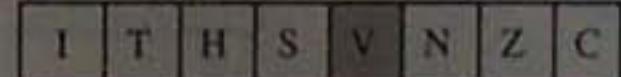

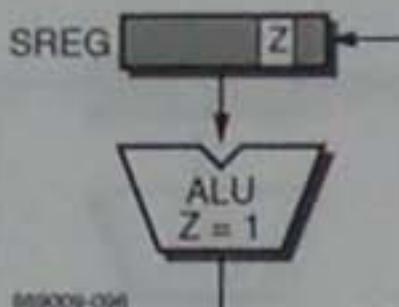

Das Status-Register (SREG) gibt Auskunft über den Status der CPU (Central Process Unit) und der ALU. Es befindet sich an der I/O-Register-Adresse \$3F bzw. im Datenspeicheradreßraum an Adresse \$5F (Bild 2.6).

Bild 2.6:

Status-Register

(SREG).

| Bit         | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------------|---|---|---|---|---|---|---|---|

| \$3F (\$5F) | I | T | H | S | V | N | Z | C |

Den einzelnen Bits sind sogenannte Flags zugeordnet, die folgende Bedeutung haben:

| Flag | Bedeutung                                                      |

|------|----------------------------------------------------------------|

| I    | Global Interrupt Enable                                        |

| T    | Bit Copy Storage                                               |

| H    | Half Carry Flag                                                |

| S    | Sign Flag, $S = N \oplus V$ für vorzeichenbehaftete Vergleiche |

| V    | Zwierkomplement-Überlauf-Flag                                  |

| N    | Negative-Flag                                                  |

| Z    | Zero-Flag                                                      |

| C    | Carry-Flag                                                     |

## 2.4 Peripherie

### 2.4.1 I/O-Ports

Die AVR-Mikrocontroller verfügen über eine unterschiedliche Anzahl an I/O-Leitungen. Die Anzahl der I/O-Leitungen reicht dabei von 5 beim AT90S2323/2343 bis 48 beim ATmega103/603 (siehe Tabelle 2.1). Einige Mikrocontroller verfügen über insgesamt 6 Ports, die alphabetisch nummeriert werden. In Tabelle 2.3 ist aufgelistet, welcher AVR-Mikrocontroller-Typ über welche Ports verfügt.

Tabelle 2.3:

Verfügbare

Ports der AVR-

Mikrocontroller.

| Typ            | Port A | Port B | Port C | Port D | Port E | Port F |

|----------------|--------|--------|--------|--------|--------|--------|

| AT90S1200      | -      | ja     | -      | 7-Bit  | -      | -      |

| AT90S2313      | -      | ja     | -      | 7-Bit  | -      | -      |

| AT90S2323/2343 | -      | 5-Bit  | -      | -      | -      | -      |

| AT90S4414/8515 | ja     | ja     | ja     | ja     | -      | -      |

| AT90S4434/8535 | -      | ja     | ja     | ja     | -      | -      |

| ATmega103/603  | ja     | ja     | ja     | ja     | ja     | ja     |

Alle Ports, bis auf Ausnahme des Port F, sind bi-direktionale Ports. Das heißt, sie dienen als Ein- und Ausgangsleitungen. Hingegen ist Port F nur als Eingang verwendbar.

Zur Definition, ob es sich bei den Ports A bis E um Ein- oder Ausgänge handelt, existiert für jeden dieser Ports ein Data Direction Register (DDR), das die Richtung jedes einzelnen Port-Pins angibt. Ferner kann bei jedem einzelnen Port-Pin getrennt ein Pull-Up-Widerstand zugeschaltet werden. Aus Tabelle 2.4 ersieht man die Richtung und den Zustand des Pull-Up-Widerstands.

| DDRXn | PORTXn | I/O     | Pull-Up | Bemerkung                                                                     |

|-------|--------|---------|---------|-------------------------------------------------------------------------------|

| 0     | 0      | Eingang | nein    | Hochohmig (Tri-state)                                                         |

| 0     | 1      | Eingang | ja      | PXn treibt Strom über internen Pull-Up-Widerstand, falls am Eingang low liegt |

| 1     | 0      | Ausgang | nein    | Aktiv low am Ausgang                                                          |

| 1     | 1      | Ausgang | nein    | Aktiv high am Ausgang                                                         |

**Tabelle 2.4:**

Datarichtungsregister (DDR)

Zu beachten ist, daß die einzelnen Port-Pins alternative Funktionen haben können. So kann ein AVR-Mikrocontroller einen externen Speicher ansteuern. Dazu wird der Speicher an Port A und Port C angeschlossen. Port A liefert dann gemultiplext die Daten und das untere Byte der Adresse. Port C liefert das obere Byte der Adresse. Andere Port-Pins werden für die vorhandene Peripherie wie UART oder SPI benötigt. Die alternative Funktionen der Port-Pins wird an der Stelle beschrieben, an der das entsprechende Peripherie-Modul erklärt wird.

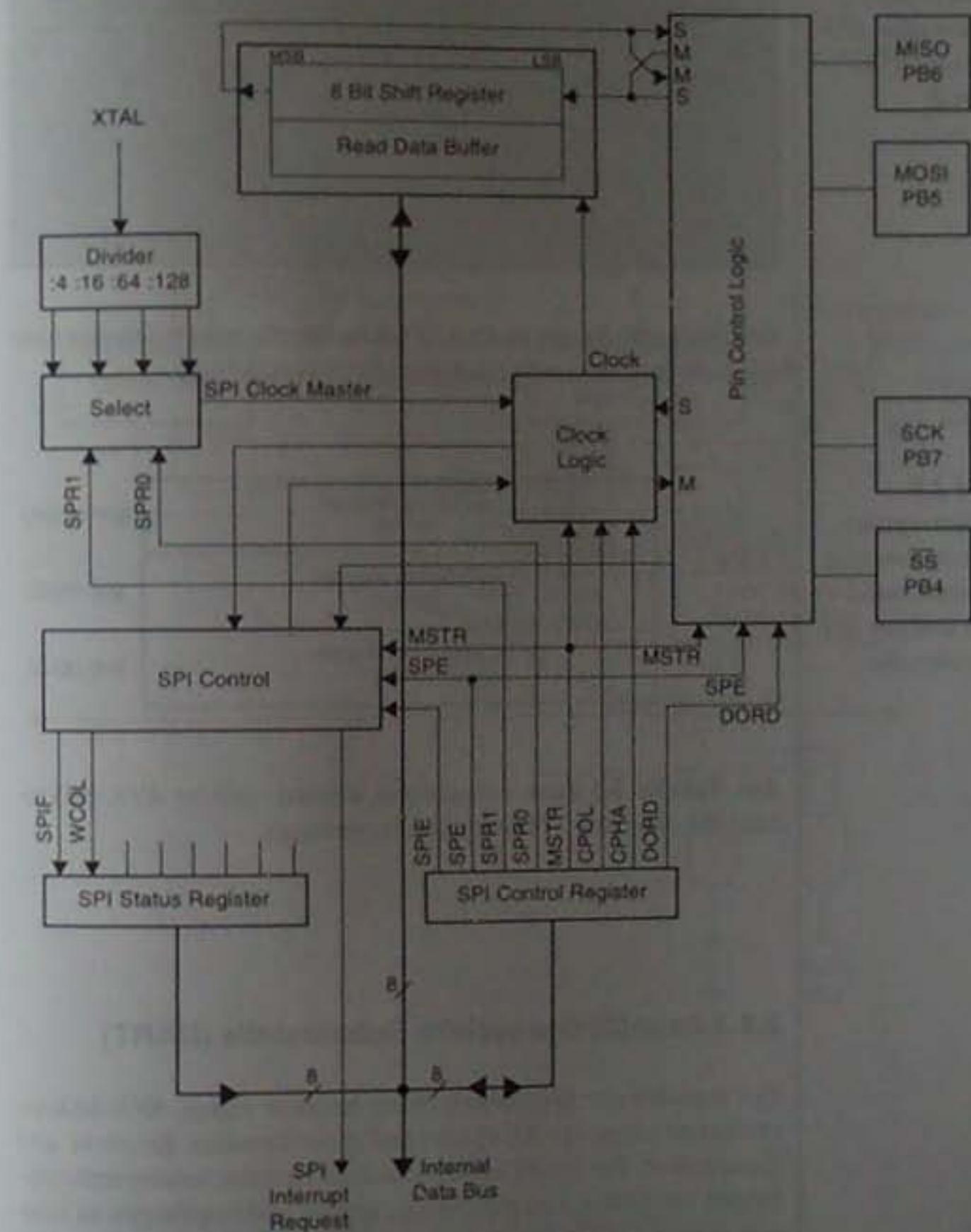

## 2.4.2 Synchrone serielle Schnittstelle (SPI)

Die SPI-Schnittstelle (Serial Peripheral Interface) dient zur schnellen synchronen Datenübertragung. In Bild 2.7 ist das Blockdiagramm der SPI-Schnittstelle zu sehen.

Die Datenübertragung geschieht über die Signale MOSI (Master Out Slave In), MISO (Master In Slave Out), SCK (Serial Clock) und bei mehreren Teilnehmer auf dem Bus noch zusätzlich mit /SS (Slave Select). Zum Anschluß der AVR-Mikrocontroller an eine SPI-Schnittstelle werden einige Pins des Port B verwendet, die dann eine alternative Funktion haben (siehe Tabelle 2.5).

Bild 2.7: Blockdiagramm SPI-Schnittstelle.

**Tabelle 2.5:**

Alternative SPI-Belegung des Port B.

| Signal | AT90S4414/4434/8515/8535 | Atmega103/603 |

|--------|--------------------------|---------------|

| MOSI   | PB5                      | PB2           |

| MISO   | PB6                      | PB3           |

| SCK    | PB7                      | PB1           |

| /SS    | PB4                      | PB0           |

Der Datentransfer von und zur SPI-Schnittstelle wird byteweise über spezielle Register im I/O-Adressraum bewerkstelligt.

**Bild 2.8:**

Steuerregister zum byteweisen Datentransfer von und zur SPI-Schnittstelle.

|                           |              |

|---------------------------|--------------|

| SPI Data Register SPDR    | \$0F (\$32F) |

| SPI Status Register SPSR  | \$0E (\$2E)  |

| SPI Control Register SPCR | \$0D (\$2D)  |

Aus Tabelle 2.1 kann entnommen werden, welche AVR-Mikrocontroller über eine SPI-Schnittstelle verfügen.

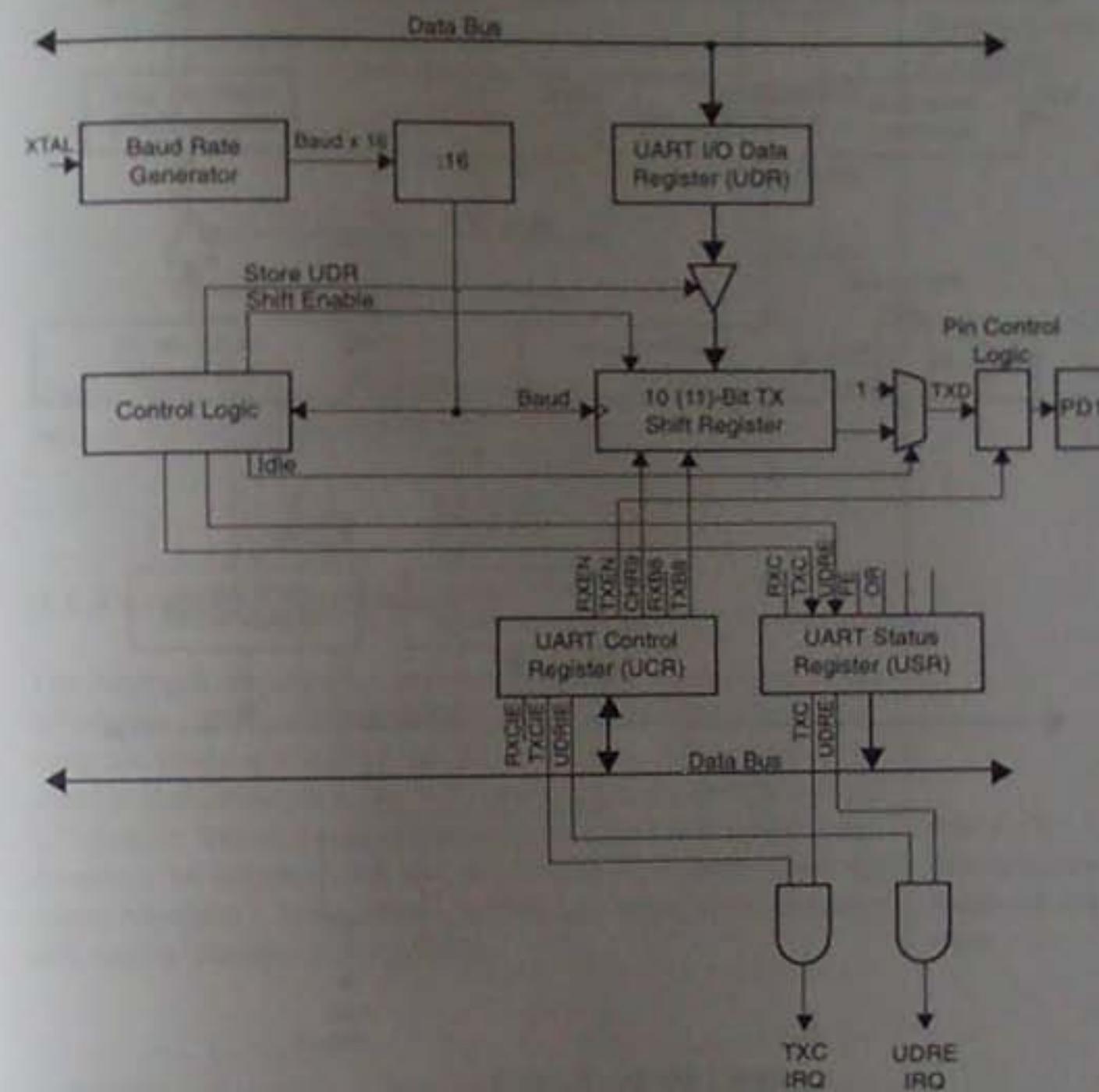

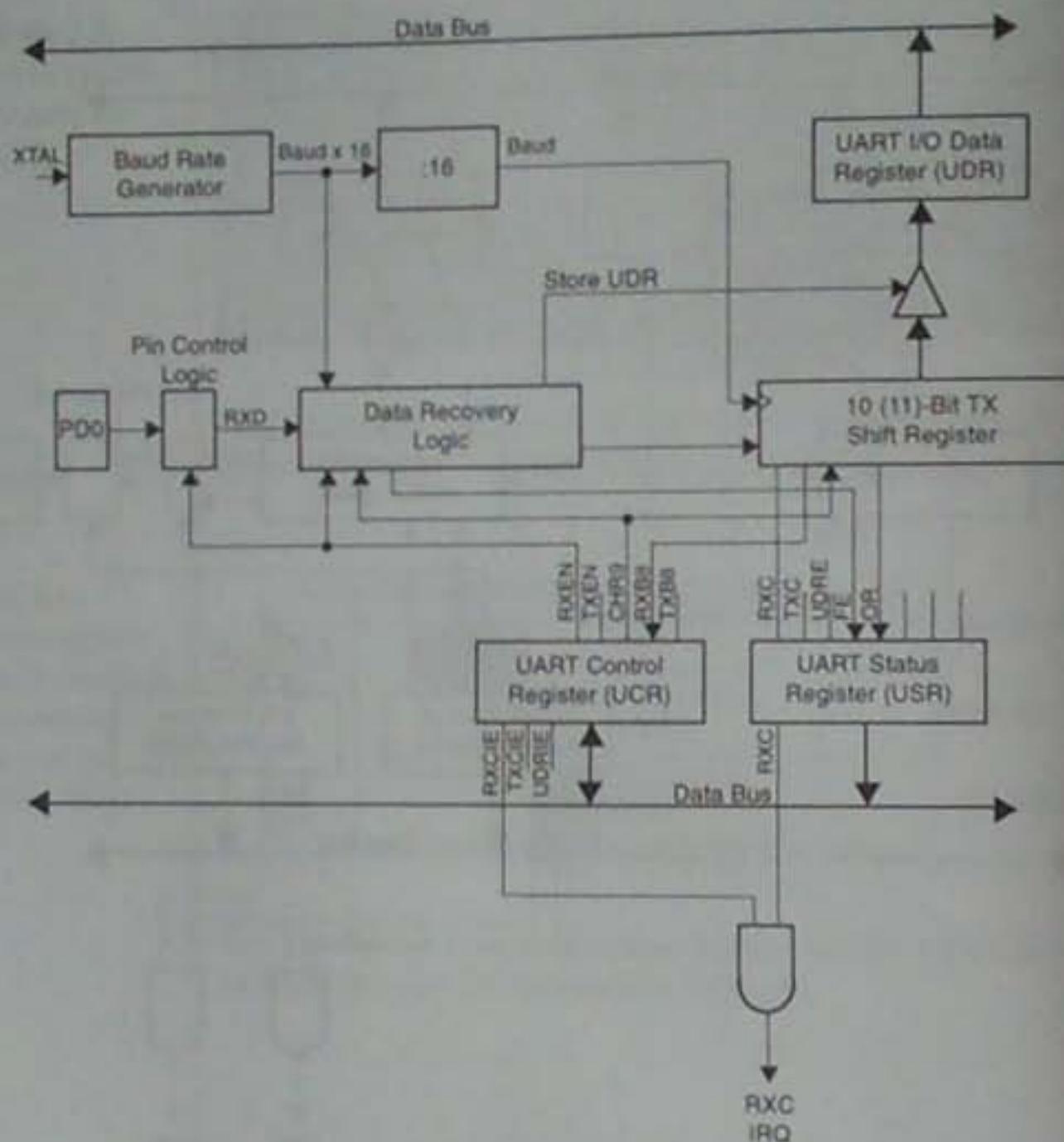

### 2.4.3 Asynchrone serielle Schnittstelle (UART)

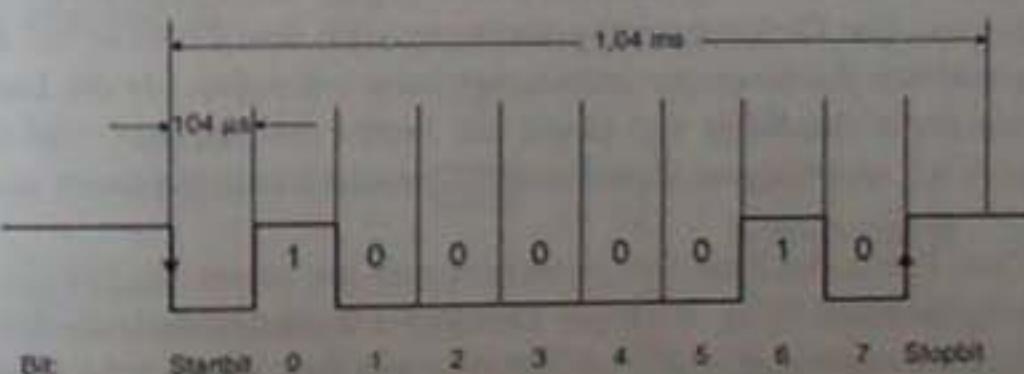

Zur asynchronen Datenübertragung besitzen einige AVR-Mikrocontroller einen UART (Universal Asynchronous Receiver and Transmitter). Der UART ermöglicht das byteweise senden und empfangen von Daten. Um gleichzeitig senden und empfangen zu können, besitzt der UART einen Transmitter (Bild 2.9) und einen Receiver (Bild 2.10), die unabhängig voneinander arbeiten.

**Bild 2.9:** Der UART Transmitter.

Bild 2.10: Der UART Receiver

Die Baudratengenerierung übernimmt der UART selber. Dazu muß der Anwender nur die entsprechende Konstante in ein Steuerregister laden. Gesteuert wird der UART über vier spezielle Register im I/O-Adressraum.

**Bild 2.11:**

Steuerregister

des UART-

Ein ausführliches Programmierbeispiel zur Ansteuerung des UART ist in Abschnitt 5.6 abgedruckt.

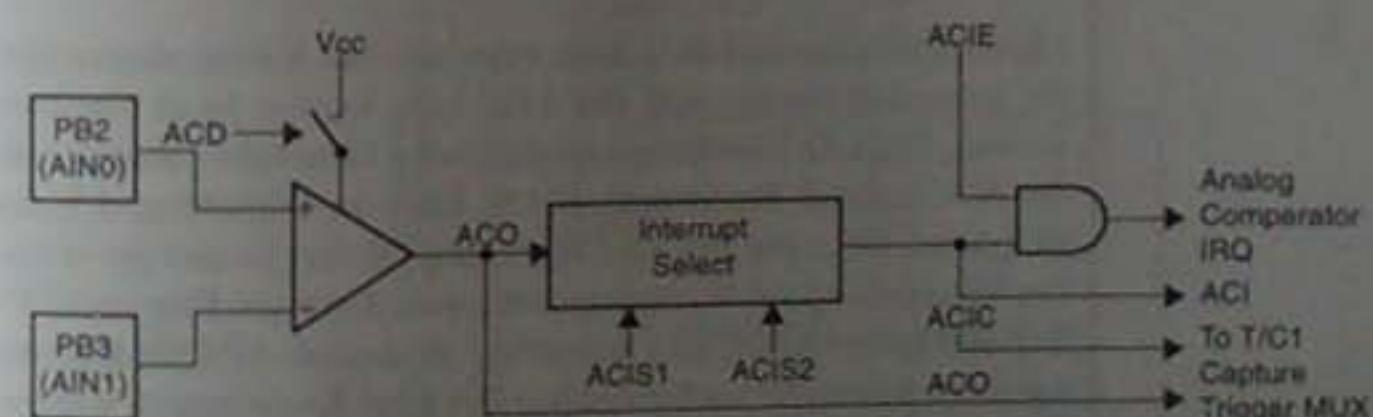

#### 2.4.4 Analog-Komparator

Der Analog-Komparator vergleicht die Eingangsspannungen an den Eingängen AIN0 (AC+) und AIN1 (AC-) miteinander. Ist die Spannung am Eingang AIN0 größer als am Eingang AIN1, so wird der Analog-Komparatorkanal ACO (Analog Comparator Output) auf „1“ gesetzt. Dieser Ausgang kann dazu benutzt werden den Timer/Counter1 zu triggern oder, um den Analog-Komparator-Interrupt (siehe Abschnitt 2.7) auszulösen. In **Bild 2.12** ist das Blockdiagramm des Analog-Komparators abgebildet.

**Bild 2.12:**

Blockdiagramm

Analog-Kompa-

rator

Gesteuert wird der Analog-Komparator über das Analog Comparator Control and Status Register (ACSR) an Adresse \$08 im I/O-Adresse Raum bzw. an Adresse \$28 im Datenspeicheradreßraum.

Die alternative Pinbelegung für die unterschiedlichen AVR-Mikrocontroller kann man aus **Tabelle 2.6** entnehmen.

**Tabelle 2.6:**

Alternative

Pinbelegung für

den Analog-

Komparator.

| Typ                      | AIN0 (AC+) | AIN1 (AC-) |

|--------------------------|------------|------------|

| AT90S1200/2313           | PB0        | PB1        |

| AT90S4414/4434/8515/8535 | PB2        | PB3        |

| ATmega103/603            | PE2        | PE3        |

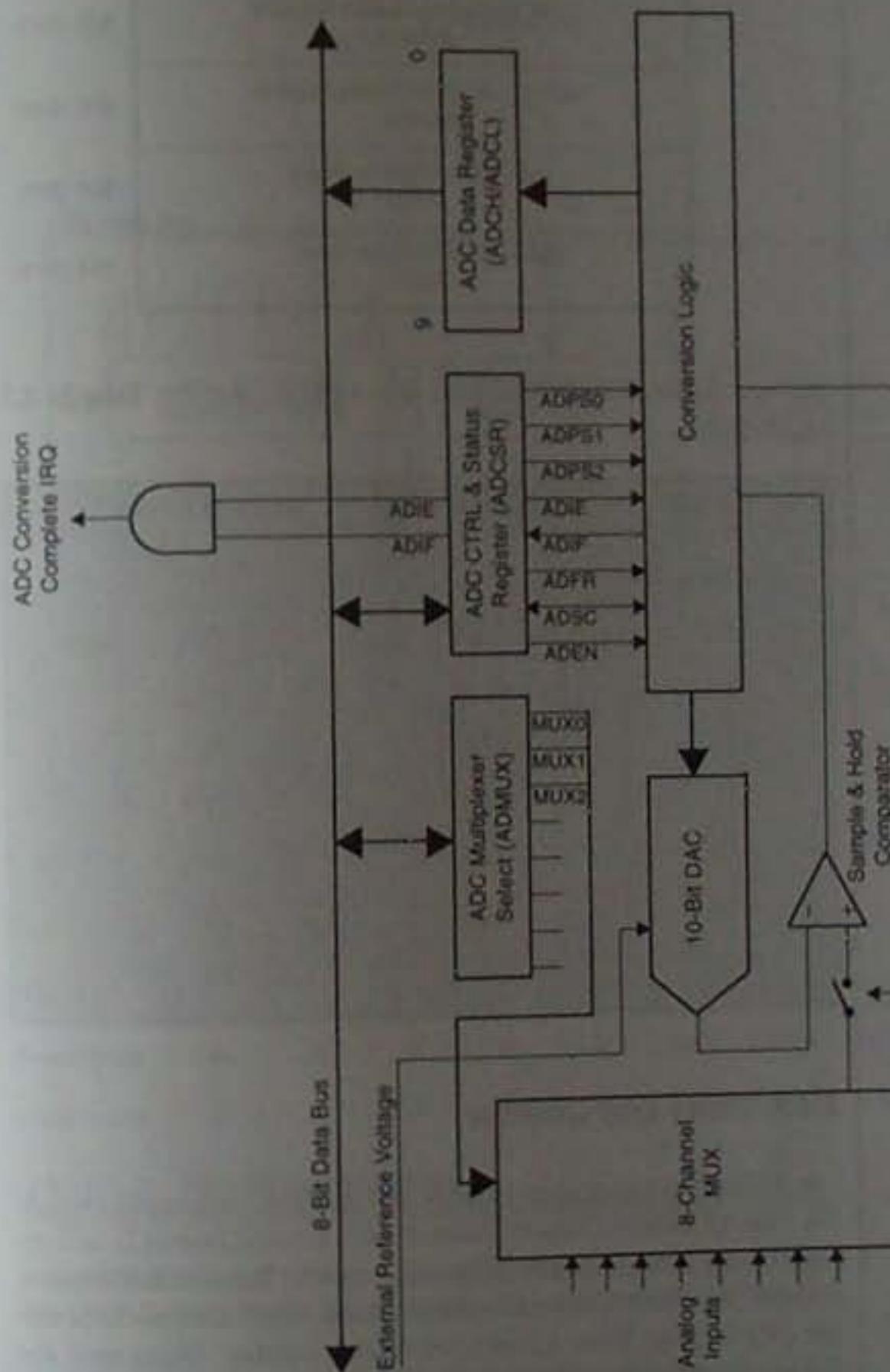

#### 2.4.5 Analog/Digital-Wandler

Die AVR-Mikrocontrollertypen AT90S4434/8535 und ATmega103/603 besitzen einen Analog/Digital-Wandler (ADC, Analog Digital Converter) mit einer Auflösung von 10-Bit. Ferner verfügt der ADC über einen 8-Kanal-Multiplexer, mit dem acht Eingänge auf den eigentlichen ADC geleitet werden können (**Bild 2.13**).

Gesteuert wird der ADC über die vier Register ADMUX, ADCSR, ADCH und ADCL im I/O-Adresse Raum (**Bild 2.14**).

Mit dem Register ADMUX wird einer der acht Kanäle ausgewählt, der gewandelt werden soll. Der ADC kann in zwei Modi betrieben werden: Die A/D-Wandlung wird durch den Anwender gestartet oder der ADC wandelt kontinuierlich. Das Ende der Wandlung, d. h. der Zeitpunkt, wenn ein analoges Signal digitalisiert ist und zur weiteren Verarbeitung zur Verfügung steht, wird durch ein Flag im ADC-Status-Register (ADCSR) angezeigt. In diesem ADCSR-Register kann der Anwender auch zwischen den zwei Betriebsmodi wählen. Das Ergebnis der A/D-Wandlung steht dann in den Registern ADCH (Bit 8 und 9) und ADCL (Bit 0 bis 7).

**Bild 2.13:** Blockdiagramm des 10-Bit ADC mit 8 Eingängen.

Bild 2.14:

Steuerregister

des ADC.

|                                          |             |

|------------------------------------------|-------------|

| ADC Multiplexer Select Register<br>ADMUX | \$07 (\$27) |

| ADC Control and Status Register<br>ADCSR | \$06 (\$26) |

| ADC Data Register (high)<br>ADCH         | \$05 (\$25) |

| ADC Data Register (low)<br>ADCL          | \$04 (\$24) |

Die alternative Port-Belegung für den ADC ist aus der Tabelle 2.7 ersichtlich.

Tabelle 2.7:

Alternative

Port-Belegung

für den Analog/

Digital-

Wandler.

| Signal | AT90S4434/8535 | Atmega103/603 |

|--------|----------------|---------------|

| ADC0   | PA0            | PF0           |

| ADC1   | PA1            | PF1           |

| ADC2   | PA2            | PF2           |

| ADC3   | PA3            | PF3           |

| ADC4   | PA4            | PF4           |

| ADC5   | PA5            | PF5           |

| ADC6   | PA6            | PF6           |

| ADC7   | PA7            | PF7           |

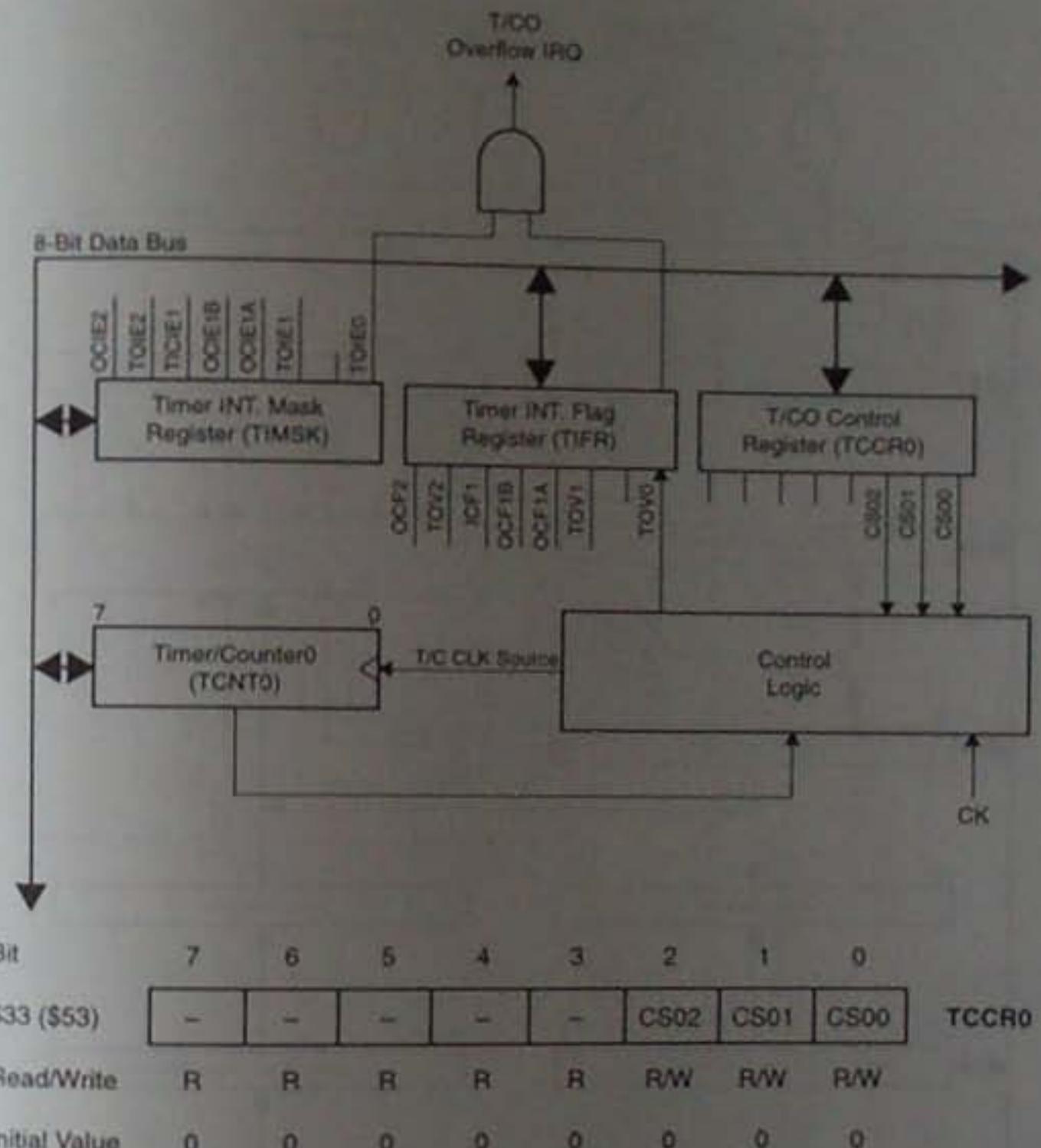

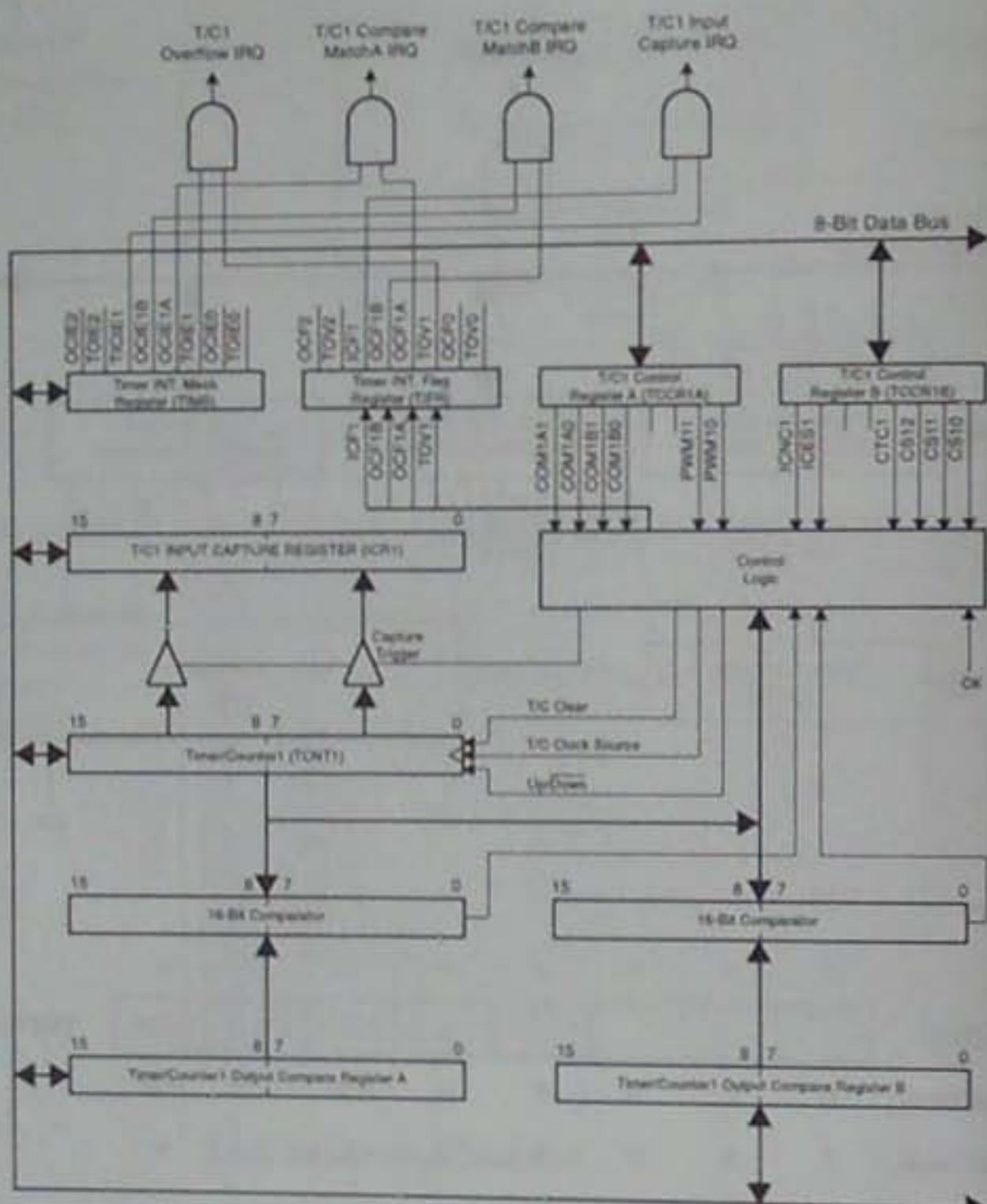

#### 2.4.6 Timer und Counter

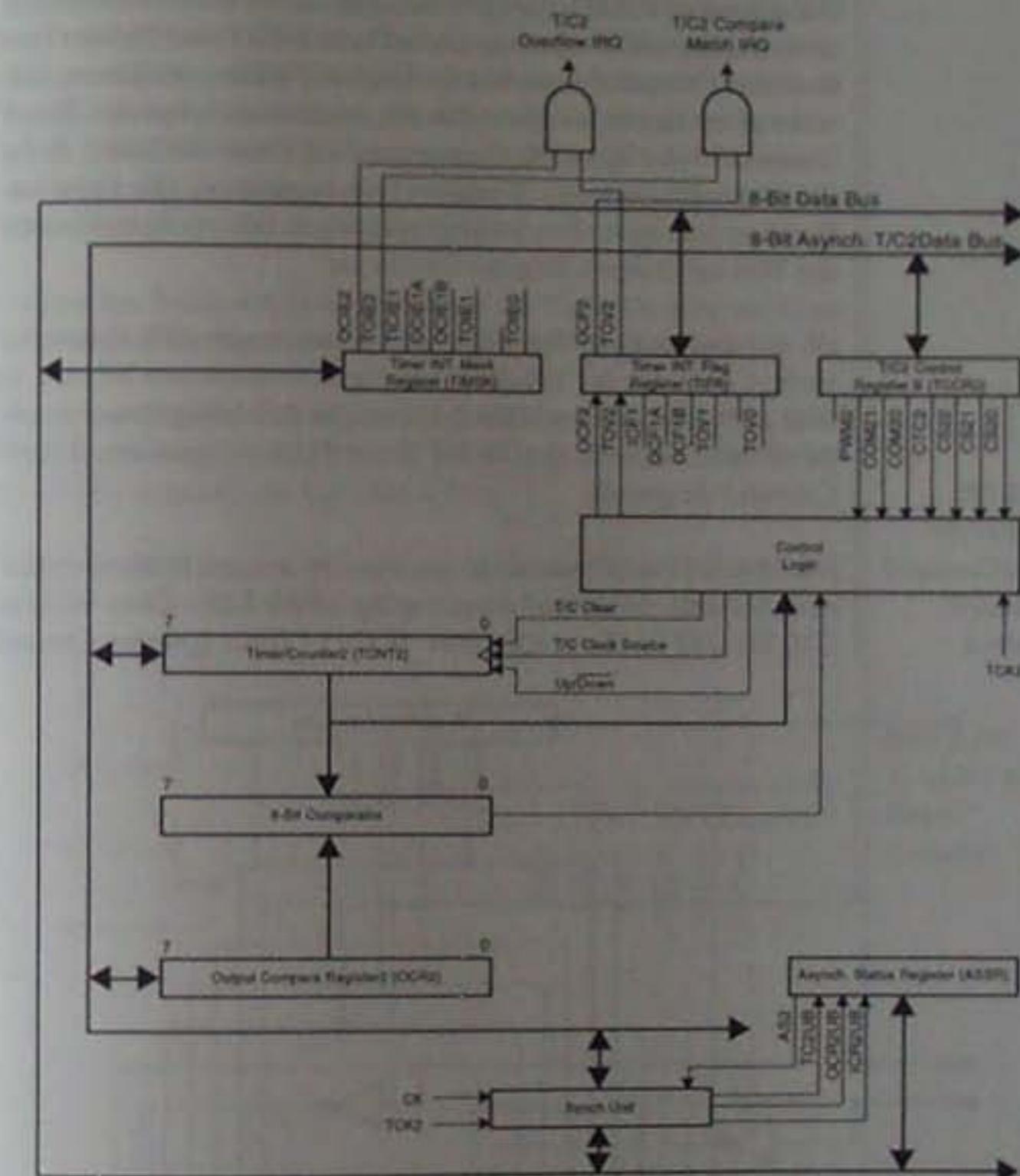

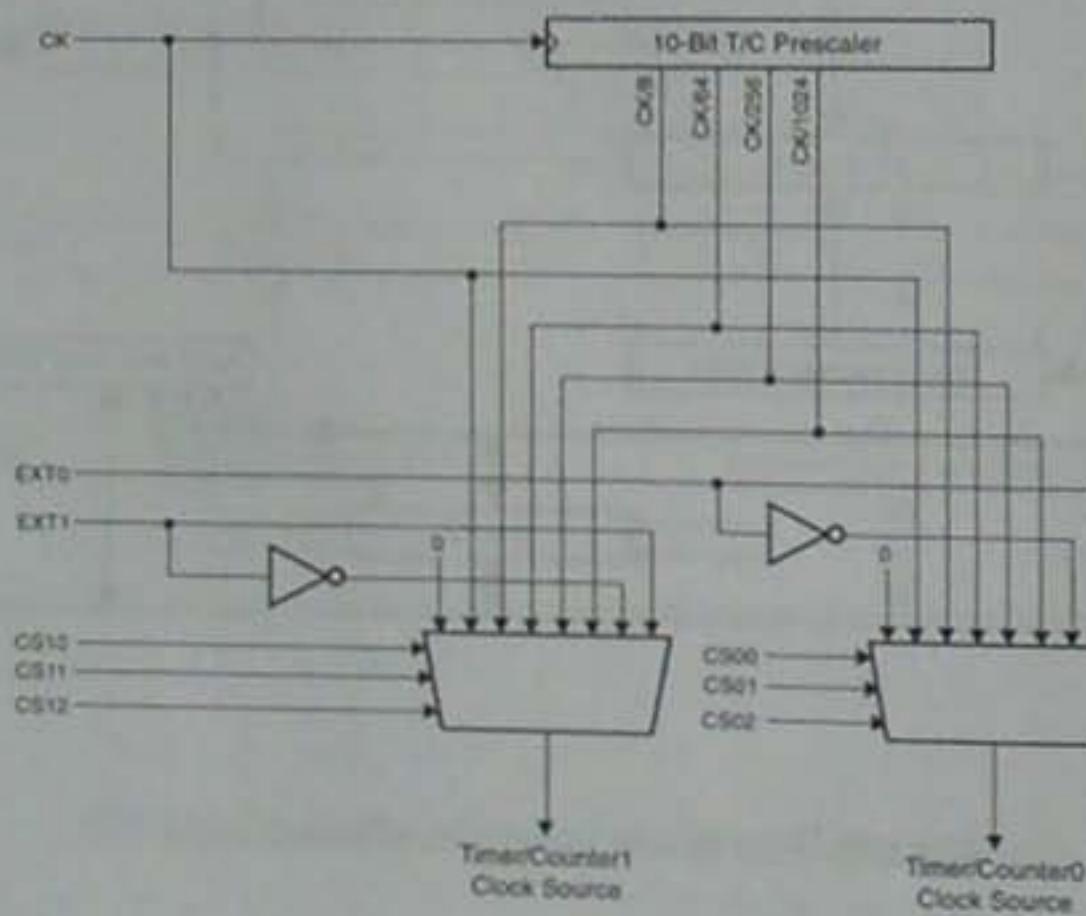

Die AVR-Mikrocontroller-Familie verfügt über insgesamt zwei 8-Bit Timer/Counter (Timer/Counter0 und Timer/Counter2) und einem 16-Bit Timer/Counter (Timer/Counter1). Bei Controllertypen, die über den Timer/Counter2 verfügen, kann dieser auch als Echtzeituhr (RTC, Real Time Clock) verwendet werden. Dazu muß ein Schwingquarz mit 32768 Hz angeschlossen werden.

- Bits 7...3 - Res: Reservierte Bits

Diese Bits sind für den AT90S4434/8535 reserviert und geben immer den Wert 0 aus

- Die Bits 2, 1 und 0 - CS02, CS01, CS00: Clock Select0, Bit 2, 1 und 0

Die Clock Select0 Bits 2, 1, 0 definieren die Vorteilerfaktor von Timer0

Bild 2.15: 8-Bit Timer/Counter0.

Bild 2.16: 16-Bit Timer/Counter1 mit Capture/Compare-Logik.

Bild 2.17: 8-Bit Timer/Counter2 mit Compare-Logik.

Bei einigen AVR-Mikrocontrollern verfügt der 16-Bit Timer/Counter1 über eine Capture/Compare-Logik und beim 8-Bit Timer/Counter2 nur über eine Compare-Logik. Mit der Capture-Funktion wird beim Auftreten einer Flanke an einem Pin der momentane Inhalt des Timer/Counter1 in ein Capture-Register gespeichert. Damit lässt sich z. B. der Zeitpunkt eines externen Signalwechsels bestimmen. Die Compare-Funktion dient dazu, einen Interrupt auszulösen, falls ein Timer/Counter den Wert im Compare-Register erreicht hat.

Ob und über welchen Timer/Counter ein bestimmter AVR-Controller verfügt, kann aus der Tabelle 2.1 (Seite 11) entnommen werden. In Bild 2.15, Bild 2.16 und Bild 2.17 sind die Blockdiagramme des 8-Bit Timer/Counter0, des 16-Bit Timer/Counter1 und des Timer/Counter2 dargestellt.

**Bild 2.18:**

Vorteiler für

Timer/Counter0

und Timer/

Counter1.

Dem 8-Bit Timer/Counter0 ist ein Vorteiler vorgeschaltet, der über eine Auswahl des Teilerfaktors verfügt (Bild 2.18). Über die Bits CS0 bis CS2 im Kontrollregister TCCR<sub>x</sub> (Timer Counter Control

Register) wird das Teilverhältnis zwischen CK/8, CK/64, CK/256 und CK/1024 des Controller-Takts eingestellt. Sollte auf dem AVR-Mikrocontroller der 8-Bit Timer/Counter0 und der 16-Bit Timer/Counter1 implementiert sein, so verfügen beide über denselben Vorteiler. Das Teilverhältnis kann aber für beider Timer/Counter unabhängig voneinander gewählt werden, da die Auswahllogik für das Teilverhältnis doppelt ausgeführt ist.

Neben den Teilverhältnissen können die Timer/Counter noch von einem externen Signal an einem Pin getaktet werden.

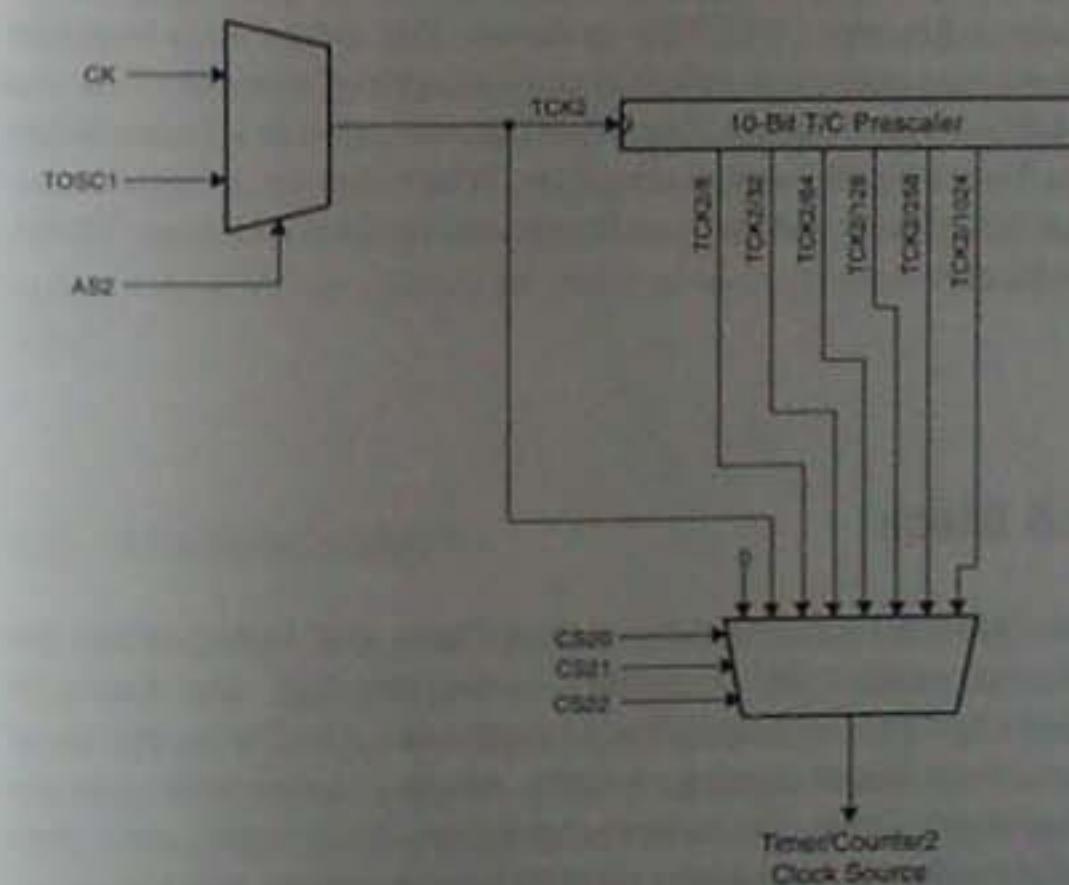

Der Timer/Counter2 verfügt über einen eigenen Vorteiler mit den Teilverhältnisse TCK2/8 bis TCK2/1024 (siehe Bild 2.19). Dabei ist TCK2 ebenfalls der Controller-Takt.

In Abschnitt 5.1 ist im Programmbeispiel der Timer/Counter0 verwendet worden, um ein Ausgangssignal einer bestimmten Dauer zu erzeugen.

**Bild 2.19:**

Vorteiler für

Timer/

Counter2.

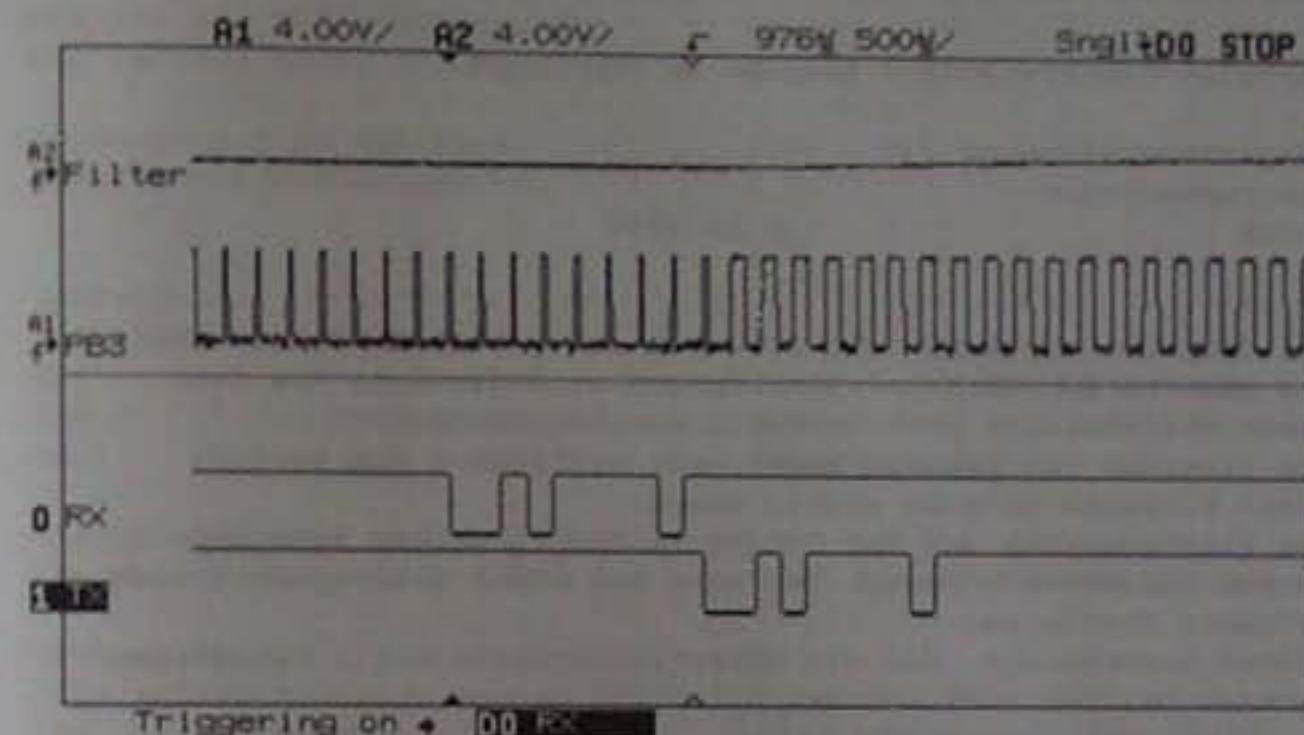

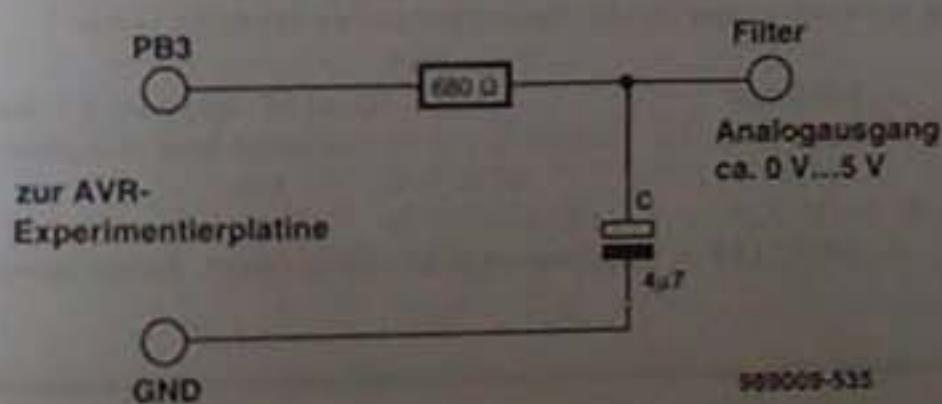

Einige Timer/Counter-Module können im PWM-Modus (Pulse Width Modulator) betrieben werden. Damit ist es möglich, ein pulsweitenmoduliertes Signal zu erzeugen. Ein Beispiel dafür ist das Programm in Abschnitt 5.6. Die Anzahl der verfügbaren PWM-Kanäle bei den einzelnen AVR-Mikrocontrollern ist der Tabelle 2.1 auf Seite 11 zu entnehmen. Die Timer/Counter-Module werden über Register im IO-Adresse Raum gesteuert (siehe Tabelle 2.2, Seite 20...22).

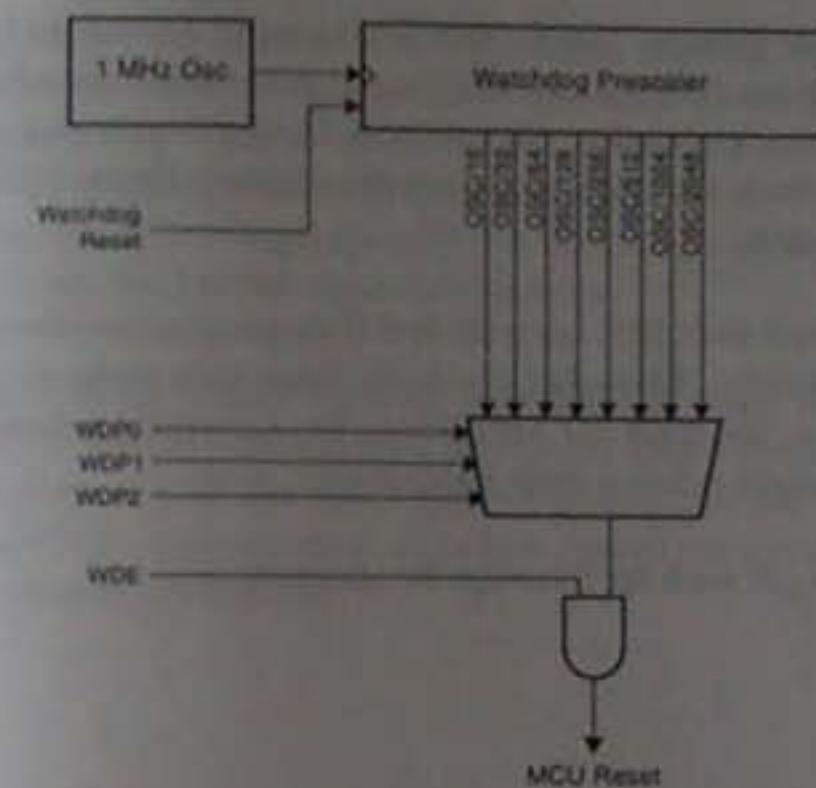

#### 2.4.7 Watchdog-Timer

Watchdog-Timer (WDT), siehe Bild 2.20 auf Seite 39, werden dazu verwendet, um zu verhindern, daß sich Mikrocontroller „aufhängen“. Das geschieht, indem ein WDT nach einer fest vorgegebenen Zeit im Mikrocontroller einen Reset auslöst und so wieder einen definierten Zustand herstellt. Der WDT wird von einem unabhängigen internen Oszillator mit 1 MHz getaktet. Zum Betrieb werden keinerlei externe zeitbestimmenden Bauelemente benötigt. Ist der WDT eingeschaltet, dies wird durch ein Bit im Watchdog-Timer-Control-Register (WDTCR) gesteuert, löst dieser nach ungefähr 16 ms (das entspricht 16000 Maschinenzyklen bei einem Takt von 1 MHz) einen Reset aus. Diese Zeit läßt sich durch das Nachschalten des Verteilers (Prescaler) erreichen. Wählt man beim Verteiler einen Teilerfaktor von 2048, so lassen sich die 16 ms auf etwa 2,048 s verlängern.

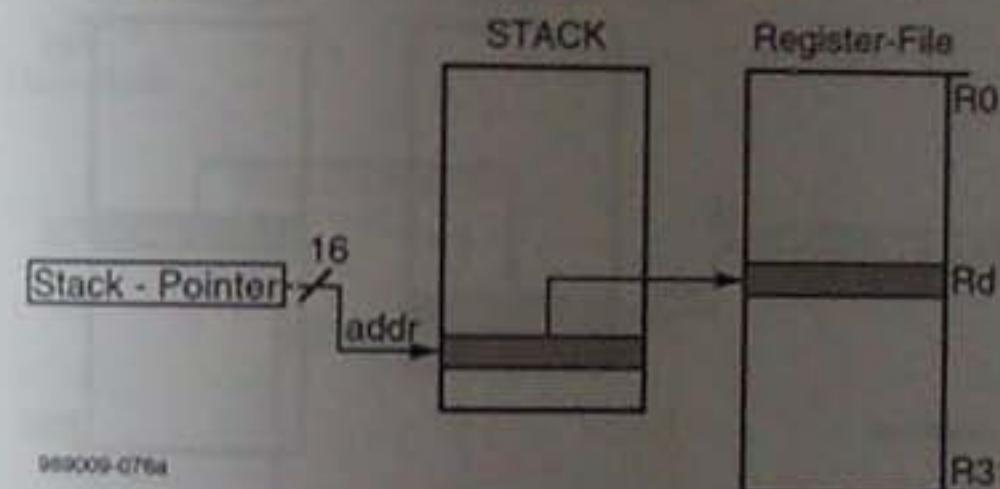

## 2.5 Stack

Der Stack ist ein Speicher, in dem Daten und insbesondere der Programmzähler (PC, Program Counter) abgelegt wird. Dabei ist dieser Speicher als Stapel (Stack) organisiert. Alle Daten, die zuerst auf diesen Stapel abgelegt werden, rutschen immer tiefer mit neu abgelegten Daten. Die zuletzt abgelegten Daten liegen ganz oben auf dem Stapel und können als erste wieder gelesen werden.

Bild 2.20:

Watchdog-

Timer mit

Verteiler.

Bei der AVR-Mikrocontroller-Familie müssen zwei unterschiedliche Arten von Stacks unterschieden werden. Zum einen der Hardware-Stack, der beim AT90S1200 implementiert ist (siehe Abschnitt 2.5.1). Zum anderen der Stack im Datenspeicher, wie er bei allen anderen AVR-Mikrocontrollern implementiert ist (siehe Abschnitt 2.5.2).

#### 2.5.1 Hardware-Stack

Der AT90S1200 verfügt als einziger AVR-Mikrocontroller über einen Hardware-Stack. Dieser ist als 3-Level-Stack ausgeführt. Ein Stack-Pointer (SP), der auf den Anfang des Stacks zeigt, wird nicht benötigt. Ein Unterprogrammaufruf (rcall) kopiert den um eins erhöhten Inhalt des Programmzählers in die oberste Ebene des Stacks. Der Inhalt der obersten Ebene des Stacks wird vorher in die nächst-

tiefere Ebene geladen. Nach einem Rücksprung aus einem Unterprogramm wird der Programmzähler mit dem Inhalt der obersten Ebene des Stacks geladen. Alle anderen Stack-Ebenen rücken um eine Ebene hoch. Der Inhalt der untersten (dritten) Ebene bleibt dabei unverändert.

Der Stack läuft über, falls mehr als drei Unterprogrammaufrufe verschachtelt werden. Wenn dies geschieht, kann nicht mehr sichergestellt werden, daß nach der Ausführung des Unterprogramms wieder zur richtigen Adresse zurückgesprungen wird.

Das gleiche gilt auch für Interrupt-Routinenaufrufe.

### 2.5.2 Stack im Datenspeicher

Mit Ausnahme des AT90S1200 liegt bei allen AVR-Mikrocontrollern der Stack im Datenspeicher. Ein Stack-Pointer zeigt dabei auf den Stack. Bevor irgendein Unterprogramm angesprungen wird, muß der Stack-Pointer initialisiert werden. Dabei legt man üblicherweise die höchste Stelle im Datenspeicher als den Anfang (oberste Ebene) des Stacks fest. Die Initialisierung des Stack-Pointers sieht folgendermaßen aus:

```

ldi SPL,LOW(RAMEND) ;lade SP low mit RAMEND(low)

ldi SPH,HIGH(RAMEND) ;lade SP high mit RAMEND(high)

```

In diesem Beispiel ist angenommen worden, daß der Stack-Pointer 16-Bit lang ist. In der ersten Zeile wird das niederwertige Byte des Stack-Pointers mit dem niederwertigen Byte der obersten Speicherstelle des Datenspeichers geladen. In der zweiten Zeile wird das höherwertige Byte des Stack-Pointers mit dem höherwertigen Byte der obersten Speicherstelle des Datenspeichers geladen.

Nach jedem Aufruf eines Unterprogramms wird der Stack-Pointer automatisch um zwei dekrementiert und nach jedem Rücksprung aus dem Unterprogramm automatisch um zwei inkrementiert. Das geschieht deshalb, weil der Programmzähler mehr als 8-Bit breit ist, der Datenspeicher hingegen nur 8-Bit breit ist. Es werden also zwei Speicherstellen im Datenspeicher benötigt.

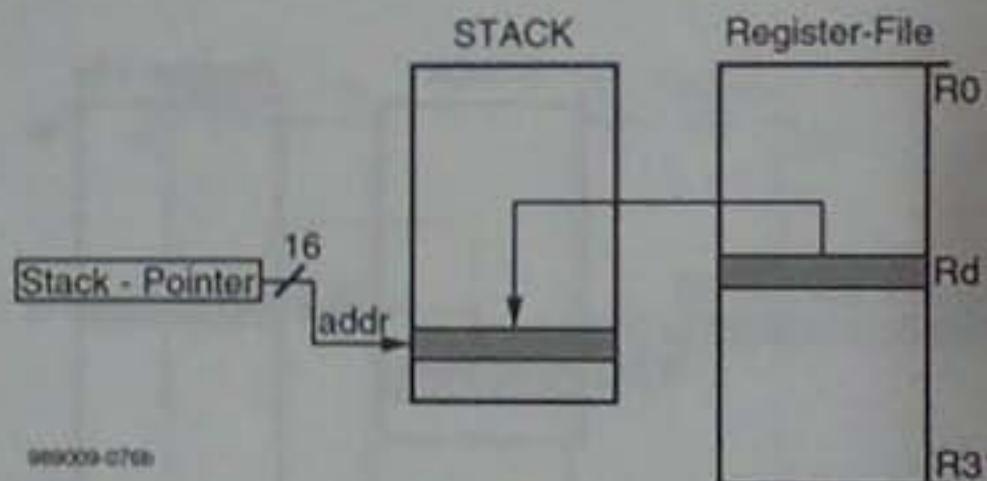

Mit dem PUSH-Befehl kann ein Byte auf dem Stack abgelegt, mit dem POP-Befehl kann ein Byte vom Stack geholt werden. Bei diesen Befehlen wird der Stack-Pointer jeweils nur um eins dekrementiert bzw. inkrementiert, da es sich jeweils nur um ein Byte und nicht zwei Bytes handelt.

### 2.6 Reset

Die AVR-Mikrocontroller-Familie verfügt über eine interne Power-On-Reset (POR) Schaltung. Für die meisten Anwendungen genügt es, den /Reset-Eingang auf die positive Versorgungsspannung  $V_{CC}$  zu legen oder offen zu lassen, da dieser Eingang bereits intern über einen Widerstand auf  $V_{CC}$  liegt. Wenn dieser Eingang beim Einschalten auf high liegt, fängt ein interner Timer an zu zählen. Dieser Timer wird vom Watchdog-Timer getaktet. Erst wenn der Endstand erreicht ist, wird der interne Reset ausgeführt. Die zeitliche Verzögerung von typisch 16 ms erlaubt es dem angeschlossenen Quarzoszillator sich zu stabilisieren.

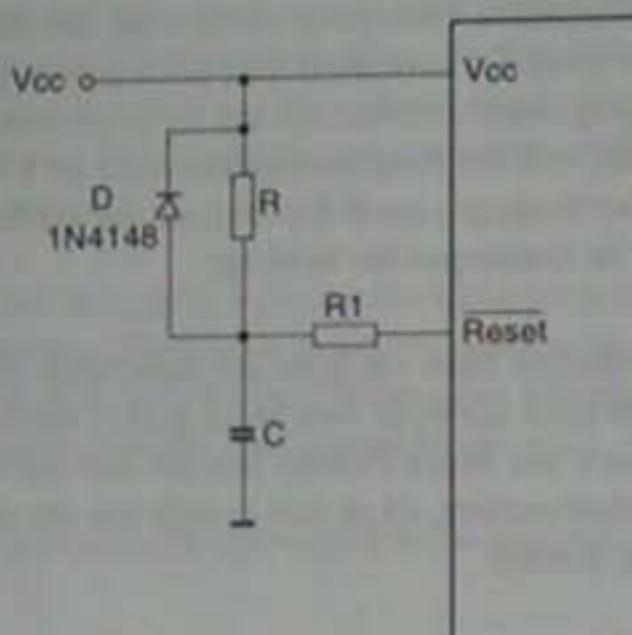

Wird ein zusätzlicher Reset benötigt, muß der Eingang /Reset beschaltet werden. Am einfachsten geschieht dies durch eine externe RC-Kombination am /Reset-Eingang (siehe Bild 2.21).

Die Zeitkonstante  $R \cdot C$  des RC-Gliedes bestimmt, wann der /Reset-Eingang auf high gelegt wird. Dabei sollte der Widerstand  $R$  kleiner als  $50\text{ k}\Omega$  gewählt werden, da sonst die Spannung am /Reset-Ein-

Bild 2.21:

Externe Reset-

Beschaltung.

gang zu klein ist. Die Diode D (1N4148) sorgt dafür, daß sich der Kondensator schnell entladen kann, wenn die Spannung ausgeschaltet wird. Der Widerstand R1 verhindert, daß bei voll aufgeladenem Kondensator ein zu hoher Strom in den /Reset-Eingang fließt. Der Wert für R1 sollte zwischen 100 Ohm und 1 KOhm liegen.

Nach jedem Reset beginnt die Programmausführung an der Adresse 0x00 im Programmspeicher (siehe Abschnitt 2.7).

## 2.7 Reset und Interrupt-Vektoren

Die ersten Stellen im Programmspeicher werden als Reset- und Interrupt-Vektoren definiert. Wird z. B. ein Reset ausgelöst, wird der Reset-Vektor an der Programmspeicheradresse 0x00 angesprungen. An dieser Stelle steht dann üblicherweise ein Sprungbefehl zur der Stelle im Programmspeicher, die nach einem Reset ausgeführt werden soll. Alle Peripherie-Module besitzen ebenfalls Vektoren, die sogenannten Interrupt-Vektoren. Löst ein Peripherie-Modul einen Interrupt aus, wird zu dem entsprechenden Interrupt-Vektor gesprun-

gen. Dort steht dann ein Sprungbefehl zur Routine (Interrupt-Handler), die diesen Interrupt behandeln soll.

Die Adressen der Interrupt-Vektoren für die verschiedenen AVR-Mikrocontroller können aus den Datenblättern, die sich als PDF-Datei auf der Begleit-CD befinden, entnommen werden.

## 2.8 Taktoszillator

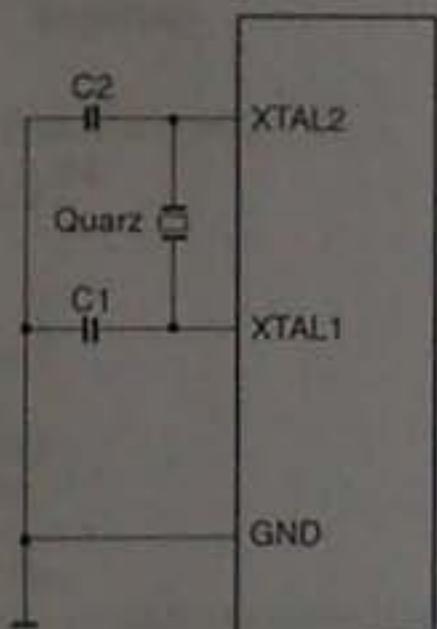

### 2.8.1 Quarz-Oszillator

Als Takt für die AVR-Controller wird üblicherweise ein Quarz-Oszillator verwendet (Bild 2.22). Dazu wird ein Schwingquarz der gewünschten Frequenz zwischen den Anschlüssen XTAL1 und XTAL2 angeschlossen. Damit der Quarz sicher anschwingt, sind noch die Kondensatoren C1 und C2 erforderlich. Diese haben einen typischen Wert von 22 pF.

Bild 2.22:

Beschaltung

eines Quarz-

Oszillators.

### 2.8.2 Interner RC-Oszillator

Der AT90S1200 kann über einen internen RC-Oszillator mit einem Takt von 1 MHz arbeiten. Dann kann der AT90S1200 ohne externe Bauteile arbeiten. Diese Betriebsart läßt sich über das Kontroll-Bit RCEN (RC Enable) im Flash-Speicher konfigurieren. Defaultmäßig ist diese Betriebsart ausgeschaltet. Sie läßt sich nur im parallelen Programmiermodus ändern.

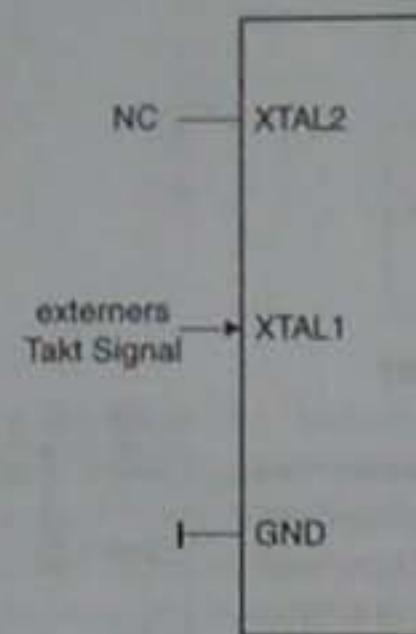

## 2.8.3 Externer Takt

Soll ein externes Takt signal verwendet werden, das z. B. von einem TTL-Taktgenerator erzeugt wird, ist die Einspeisung nach Bild 2.23 vorzunehmen.

Bild 2.23:

Externe Takt-

einspeisung.

## 2.9 Der Befehlssatz

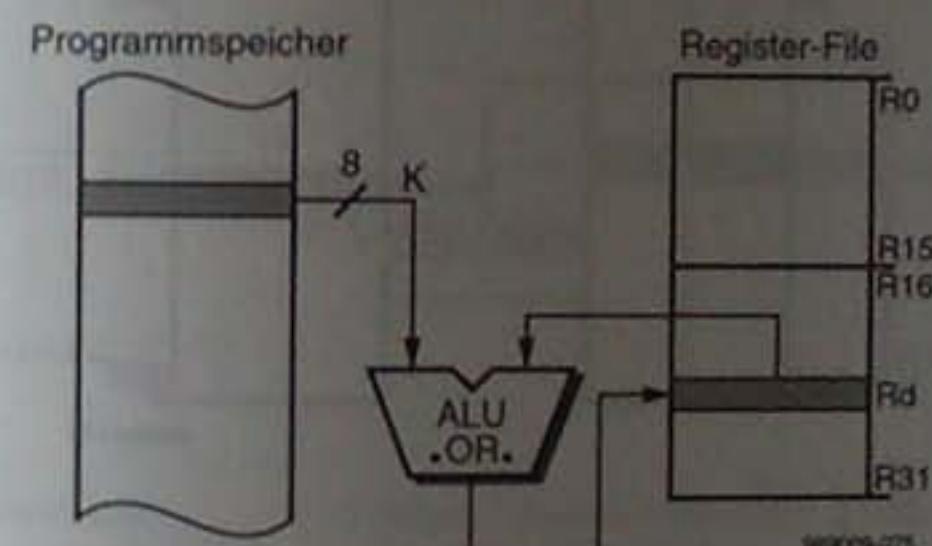

Im folgenden wird der Befehlssatz der AVR-Mikrocontroller Familie besprochen. Dazu werden noch einige Definitionen erläutert:

|        |                                                                                    |

|--------|------------------------------------------------------------------------------------|

| A      | Inhalt von A                                                                       |

| A<7:0> | Bit 0 bis 7 von A                                                                  |

| (A)    | Inhalt der Speicherstelle, auf die der Inhalt von A zeigt (indirekte Adressierung) |

| /A     | A ist invertiert zu nehmen                                                         |

| addr   | Konstante Adressdaten für Programmzähler                                           |

| bit    | Ein Bit eines Registers                                                            |

| K      | Konstante oder Datenbyte (8 Bit)                                                   |

| mask   | Maske für Bitmanipulation                                                          |

| offset | Offset zur Adresse                                                                 |

| Port   | I/O-Adresse                                                                        |

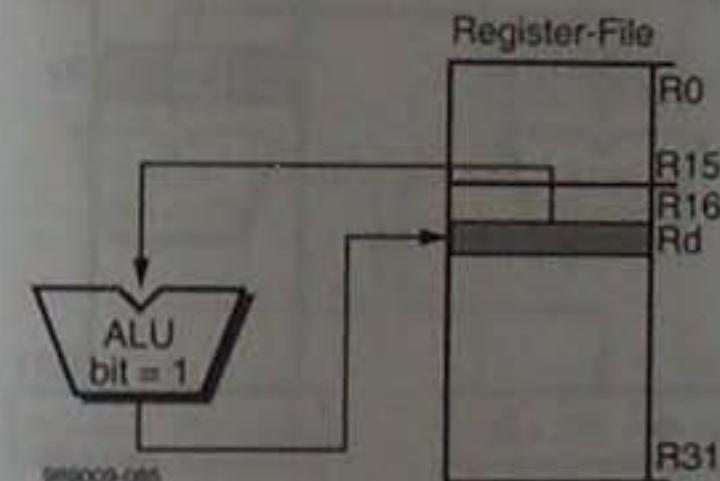

| Rd     | Ziel- und Quellregister im Register-File (GPR)                                     |

| Rr     | Quellregister im Register-File (GPR)                                               |

| ←      | Zuweisung                                                                          |

| .AND.  | UND-Verknüpfung                                                                    |

| .OR.   | ODER-Verknüpfung                                                                   |

| .XOR.  | Exklusiv-ODER-Verknüpfung                                                          |

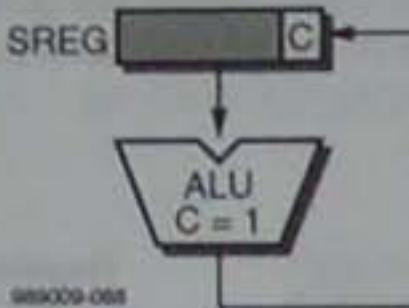

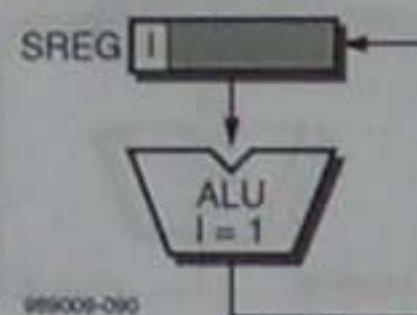

| SREG   | STATUS-Register                                                                    |

| C      | Carry-Flag im STATUS-Register                                                      |

| Z      | Zero-Flag im STATUS-Register                                                       |

| N      | Negative-Flag im STATUS-Register                                                   |

| V      | Zweierkomplement-Überlauf Flag                                                     |

| S      | Signed-Flag, S = N .XOR. V (für vorzeichenbehaftete Vergleiche)                    |

| H      | Half-Carry-Flag im STATUS-Register                                                 |

| T      | Transfer-Bit im STATUS-Register (wird von den Befehlen BLD und BST benutzt)        |

| I      | Global Interrupt Enable/Disable Flag im STATUS-Register                            |

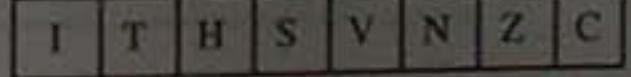

Schattierte Flächen im STATUS-Register bedeuten, daß das Flag vom Ergebnis des Befehls beeinflußt werden kann. Im unten gezeigten Beispiel werden das Zero- und Carry-Flag beeinflußt.

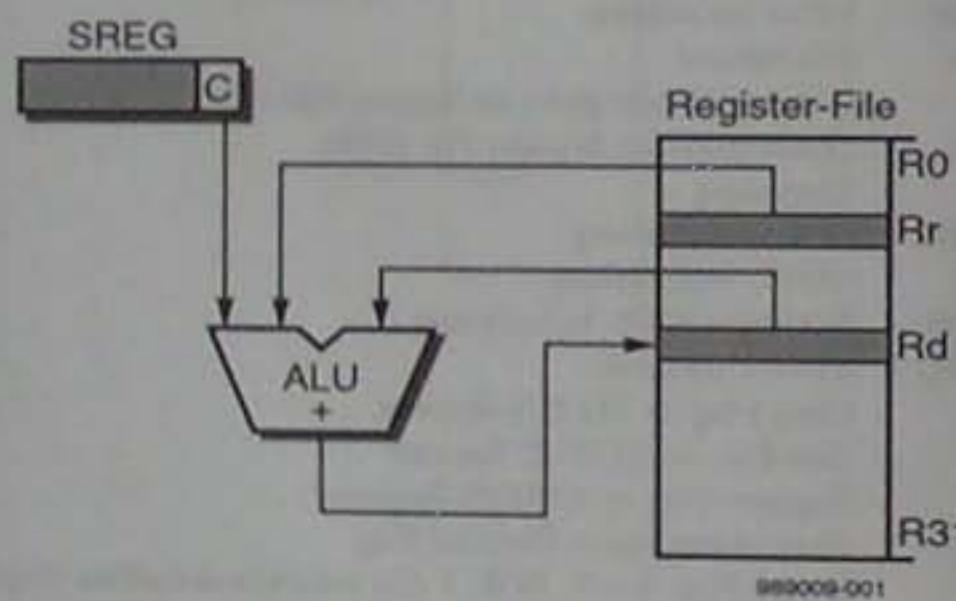

ADC Rd,Rr

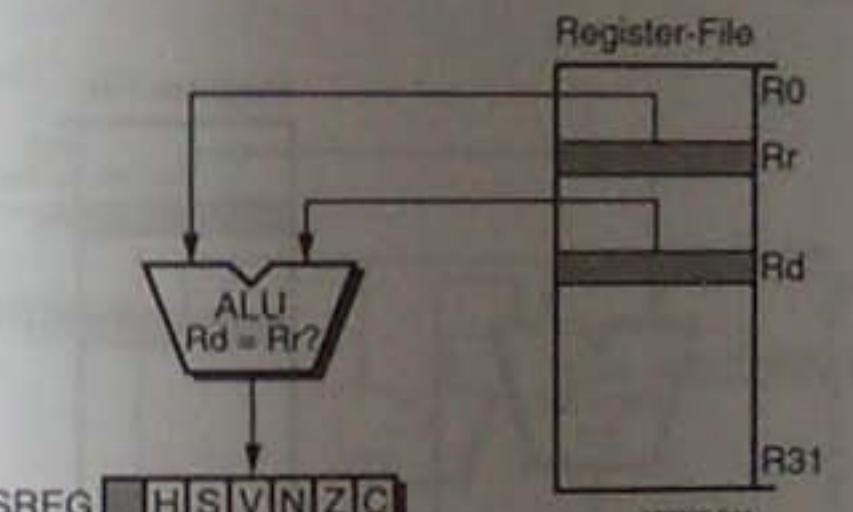

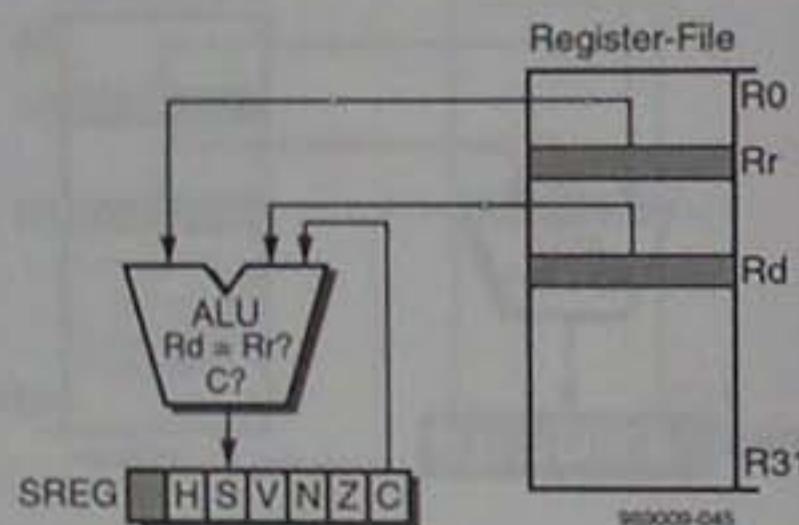

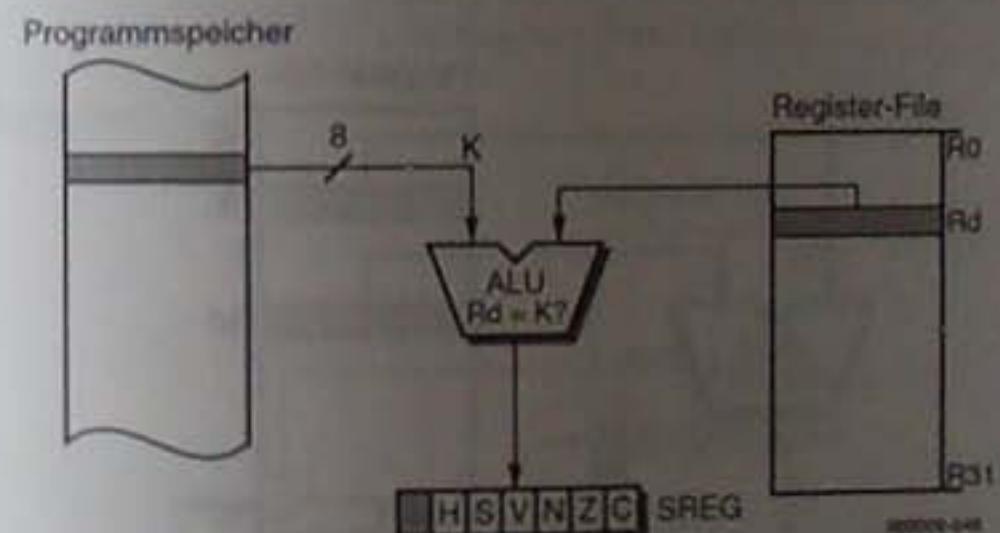

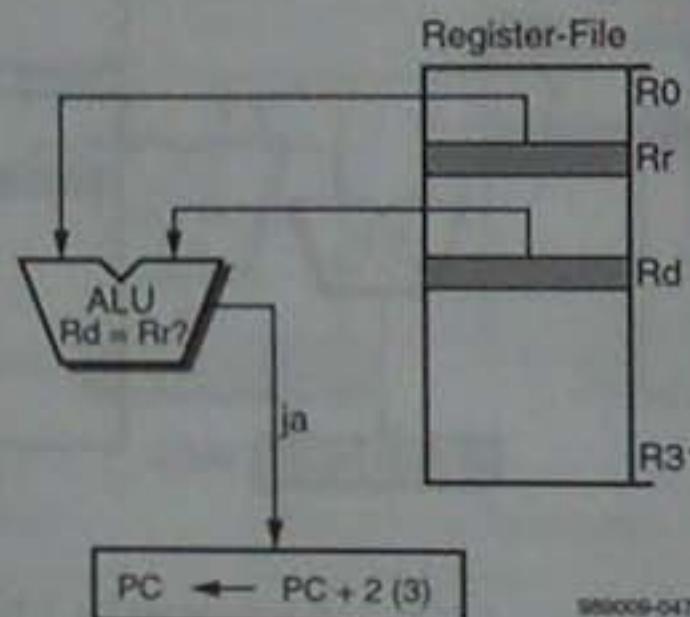

ADC Rd,Rr

Addiere Register Rr mit Carry-Flag zum Register Rd.

Funktion:

$Rd \leftarrow Rd + Rr + C$

Beschreibung:

Der Inhalt des Registers Rr und das Carry-Flag werden zum Inhalt des Registers Rd addiert. Das Ergebnis der Addition steht im Register Rd. Der Inhalt des Registers Rr bleibt unverändert. Der Befehl ist für alle Register R0 bis R31 im Register-File zulässig.

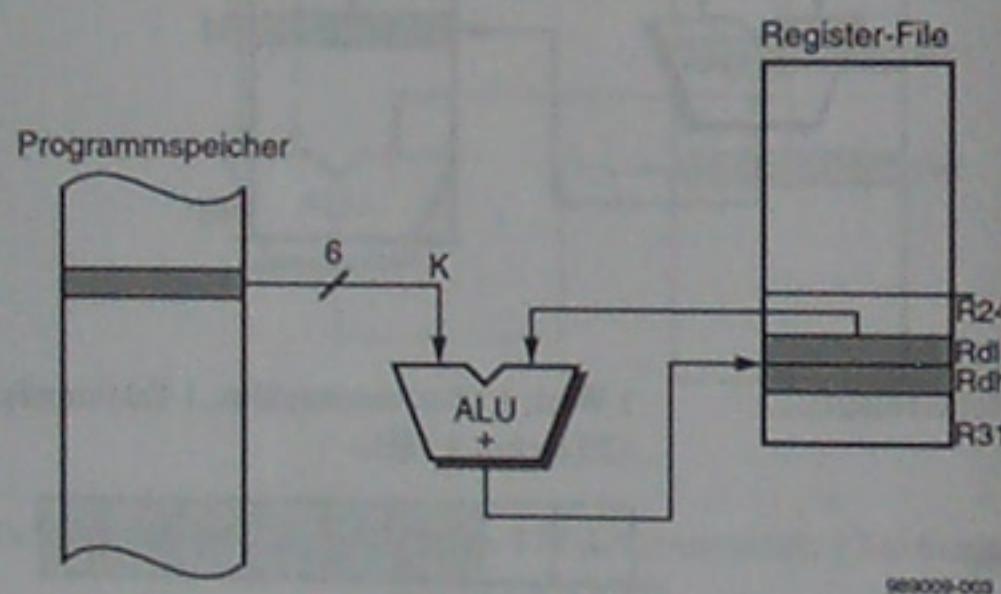

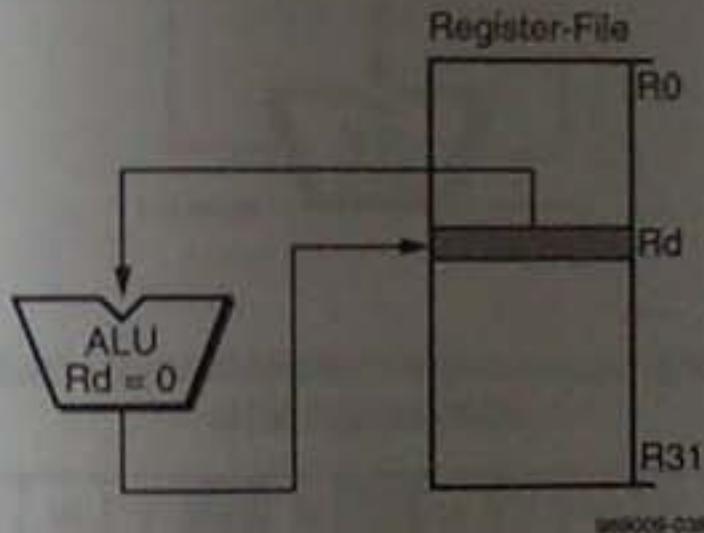

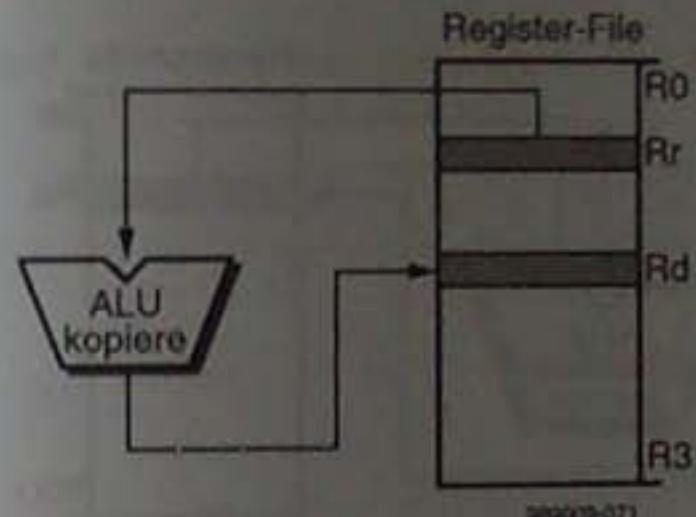

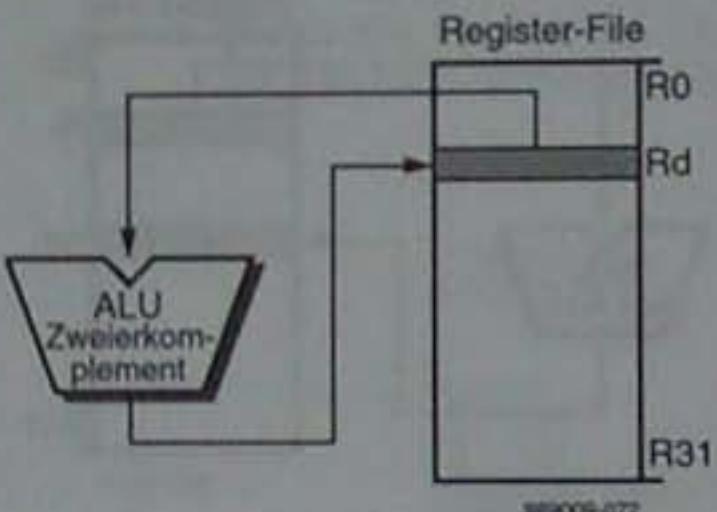

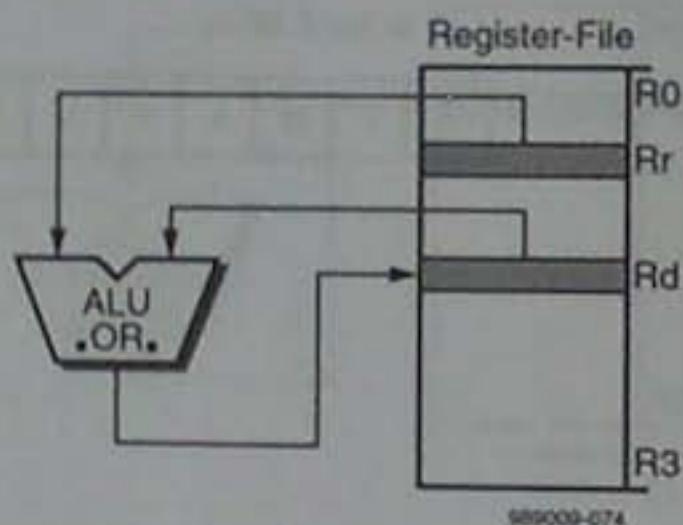

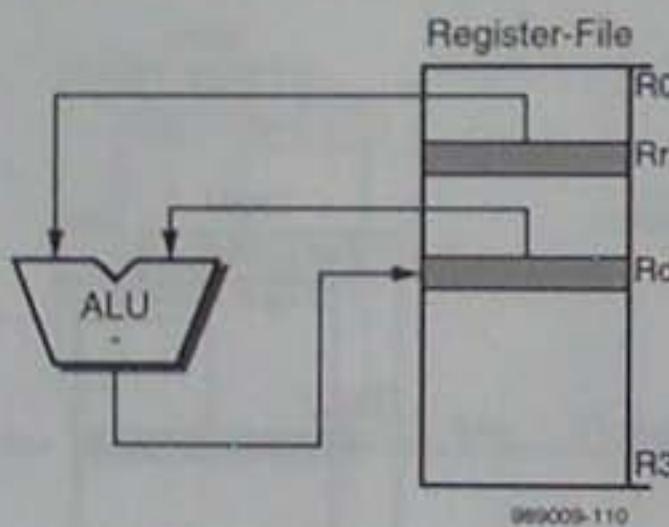

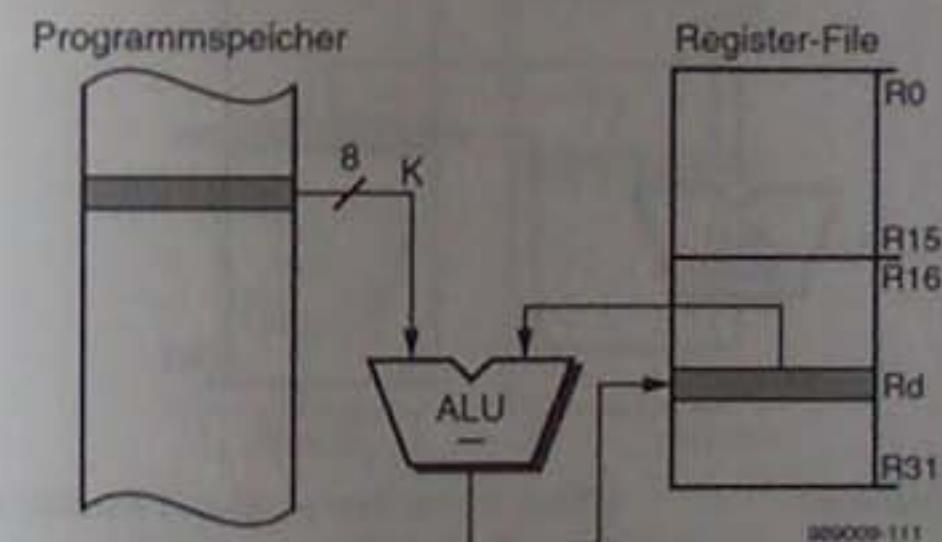

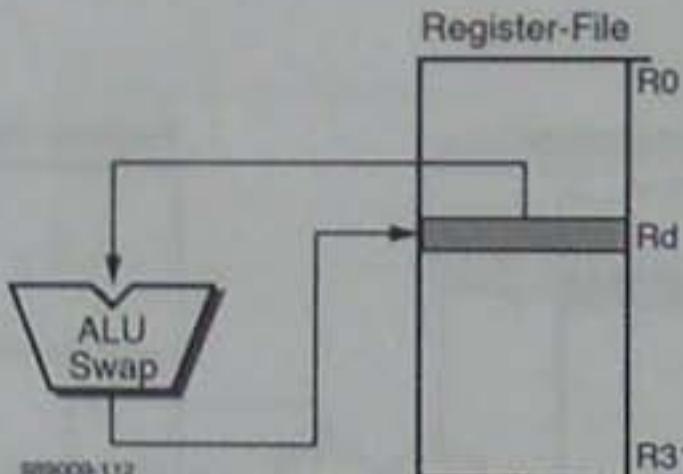

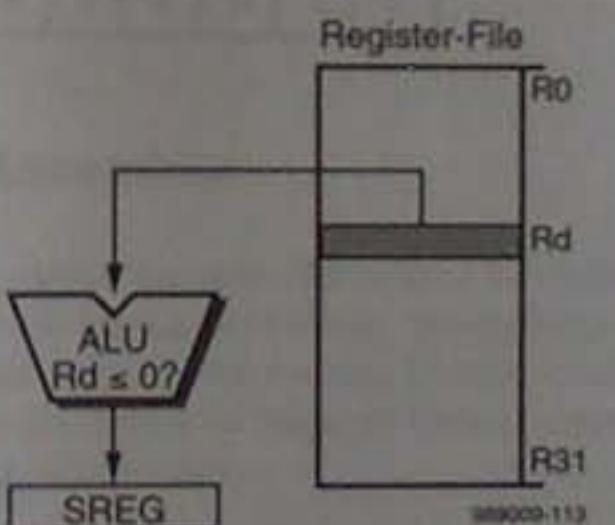

Datenfluß:

Befehlsablauf:

1 Wort, 1 Maschinenzyklus, 1 Taktimpuls:

125 ns bei 8 MHz

Flags:

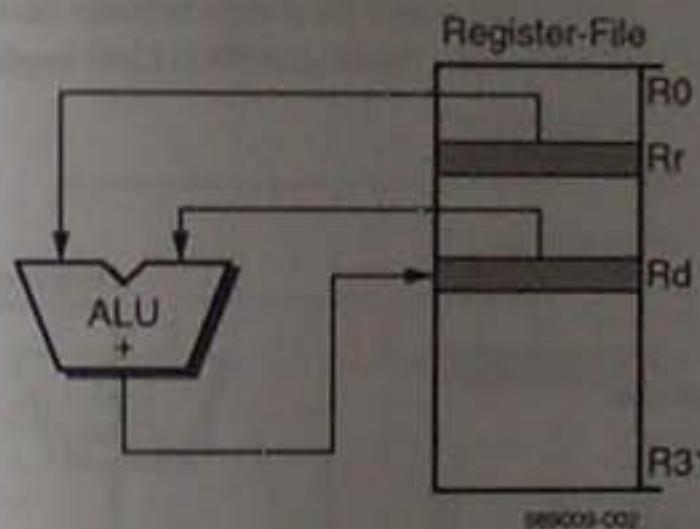

ADD Rd,Rr

Addiere Register Rr zum Register Rd.

ADD Rd,Rr

Funktion:

$Rd \leftarrow Rd + Rr$

Beschreibung:

Der Inhalt des Registers Rr wird zum Inhalt des Registers Rd addiert. Das Ergebnis der Addition steht im Register Rd. Der Inhalt des Registers Rr bleibt unverändert. Der Befehl ist für alle Register R0 bis R31 im Register-File zulässig.

Datenfluß:

Befehlsablauf:

1 Wort, 1 Maschinenzyklus, 1 Taktimpuls:

125 ns bei 8 MHz

Flags:

ADIW RdI,K

ADIW RdI,K

Addiere unmittelbaren Wert K zum Registerpaar Rdh:Rdl.

Funktion:

$Rdh:Rdl \leftarrow Rdh:Rdl + K$

Beschreibung:

Der unmittelbare Wert K (K im Bereich von 0 bis 63) wird zum Inhalt des Registerpaars Rdh:Rdl addiert. Dabei gibt Rdl das untere der beiden Register an. Gültige Werte für Rdl sind 24, 26, 28 und 30. Der Wert für Rdh ist dann automatisch 25, 27, 29 oder 31. Dieser Befehl bezieht sich also nur auf die oberen vier Registerpaare und ist somit für Zeigerbefehle bestens geeignet. (Nicht im AT90S1200 implementiert.)

Datenfluß:

Befehlsablauf:

1 Wort, 2 Maschinencyklen, 2 Taktimpulse: 205 ns bei 8 MHz

Flags:

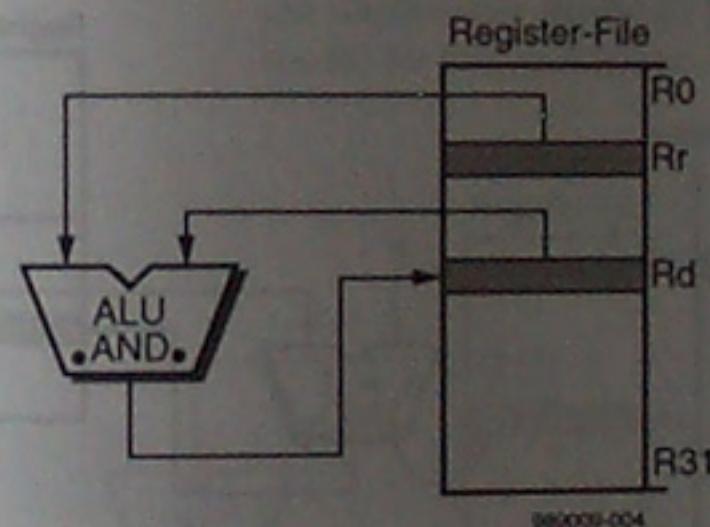

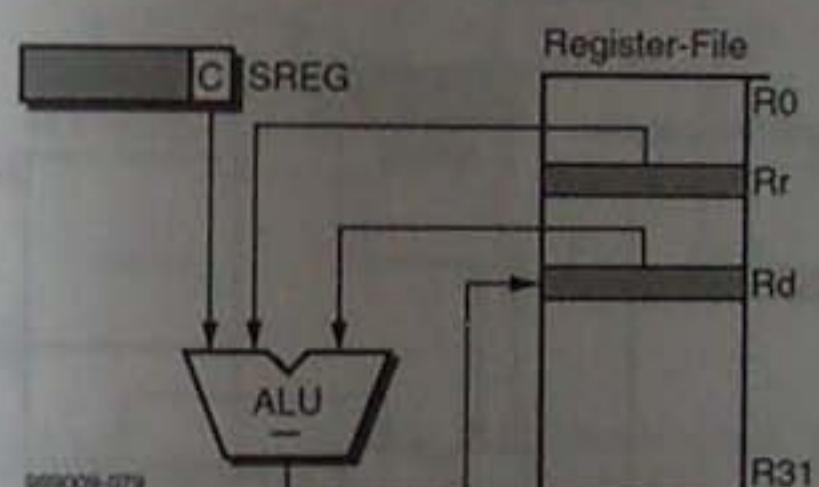

AND Rd,Rr

Register Rr und Rd logisch UND-verknüpfen.

AND Rd,Rr

Funktion:

$Rd \leftarrow Rd \cdot AND, Rr$

Beschreibung:

Der Inhalt des Registers Rr wird mit dem Inhalt des Registers Rd logisch UND-verknüpft. Das Ergebnis der Verknüpfung steht im Register Rd. Der Inhalt des Registers Rr bleibt unverändert. Der Befehl ist für alle Register R0 bis R31 im Register File zulässig.

Datenfluß:

Befehlsablauf:

1 Wort, 1 Maschinencyklus, 1 Taktimpuls: 125 ns bei 8 MHz

Flags:

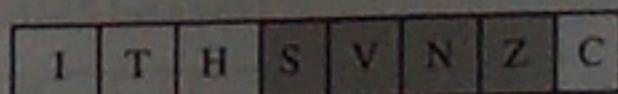

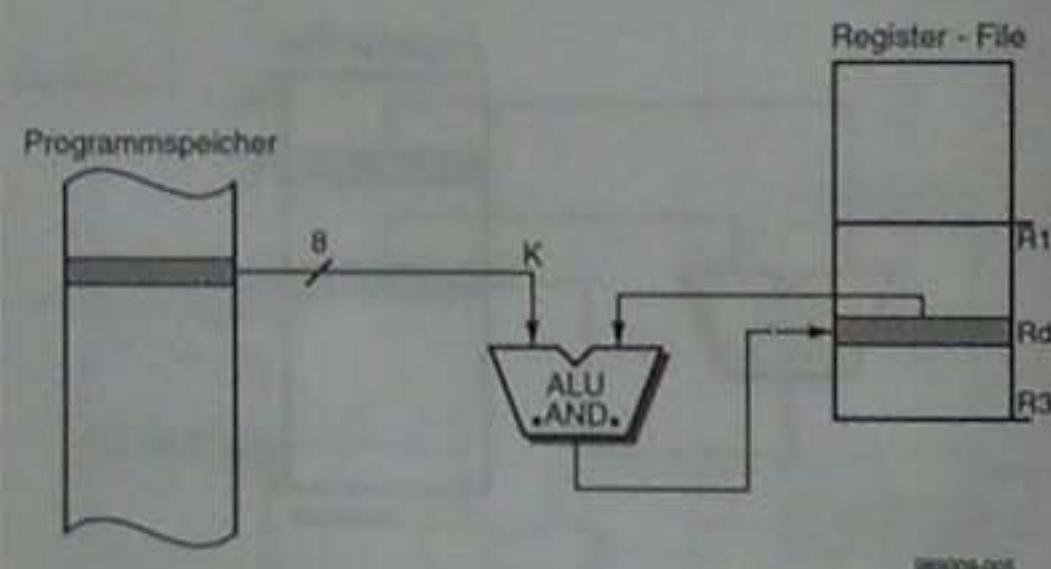

ANDI Rd,K

ANDI Rd,K

Unmittelbaren Wert K und Register Rd logisch UND-verknüpfen.

Funktion:

$Rd \leftarrow Rd \text{ AND. } K$

Beschreibung:

Der unmittelbare Wert K (K im Bereich von 0 bis 255) wird dem Inhalt des Registers Rd logisch UND-verknüpft. Das Ergebnis der Verknüpfung steht im Register Rd. Der Befehl ist für die Register R16 bis R31 in der oberen Hälfte des Register-Files zulässig.

Datenfluß:

Befehlsablauf:

1 Wort, 1 Maschinenzyklus, 1 Taktimpuls:

125 ns bei 8 MHz

Flags:

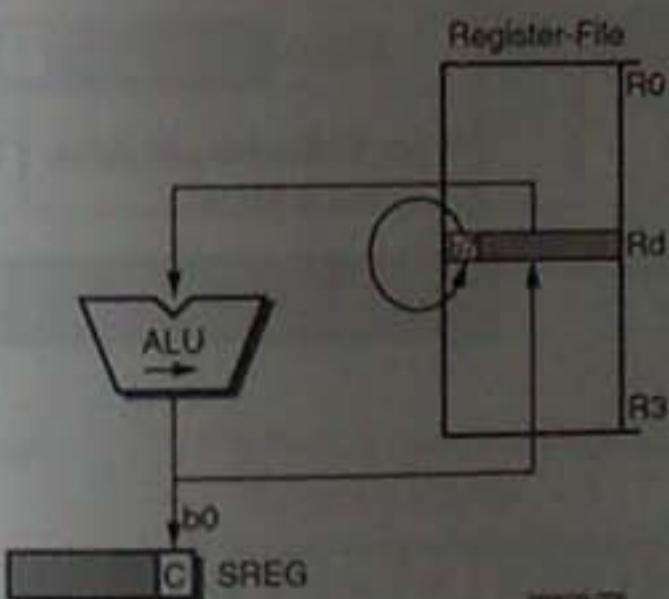

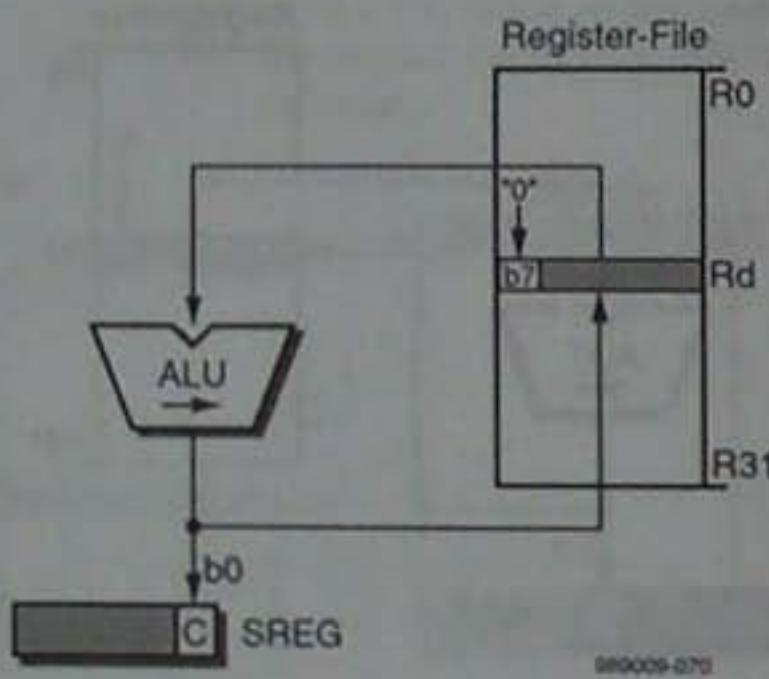

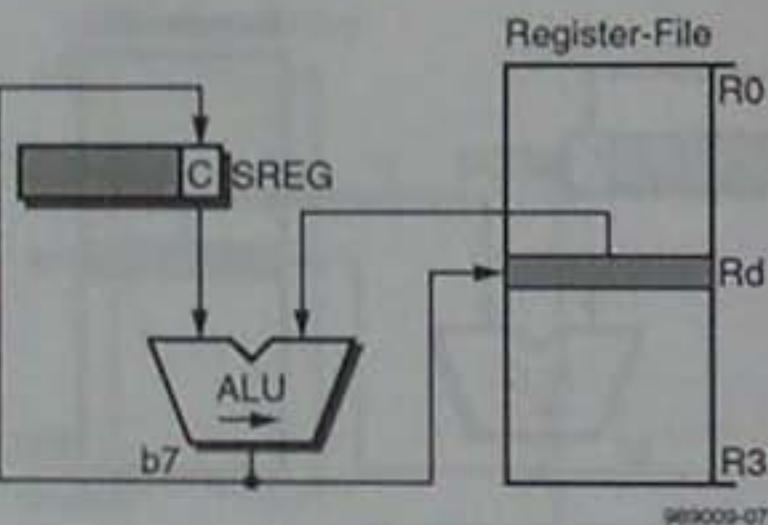

ASR Rd

Schiebe das Register Rd arithmetisch nach rechts.

Funktion:

$Rd<7> \leftarrow Rd<7>; C \leftarrow Rd<0>;$

$Rd<6> \leftarrow 0, Rd<5:0> \leftarrow Rd<6:1>$

Beschreibung:

Der Inhalt des Registers Rd wird um eine Stelle arithmetisch nach rechts geschoben. Dabei wird der Inhalt des Bit 7 erhalten, Bit 6 wird mit 0 überschrieben und der Inhalt des Bit 0 in das Carry-Flag übertragen. Dieser Befehl teilt eine Zahl, die in Zweierkomplement Schreibweise gespeichert ist, durch zwei. Dabei wird das Vorzeichen der Zahl nicht geändert. Das Carry-Flag kann zum Runden herangezogen werden. Der Befehl ist für alle Register R0 bis R31 im Register-File zulässig.

Datenfluß:

Befehlsablauf:

1 Wort, 1 Maschinenzyklus, 1 Taktimpuls:

125 ns bei 8 MHz

Flags:

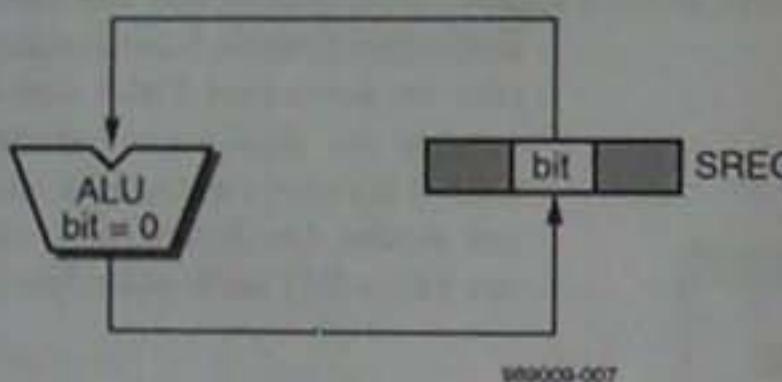

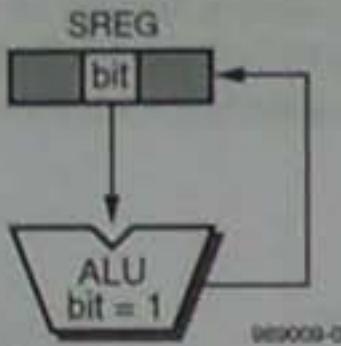

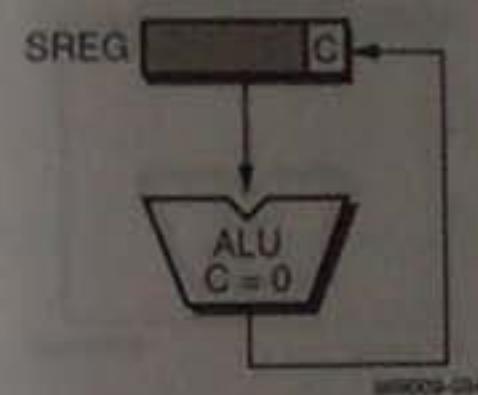

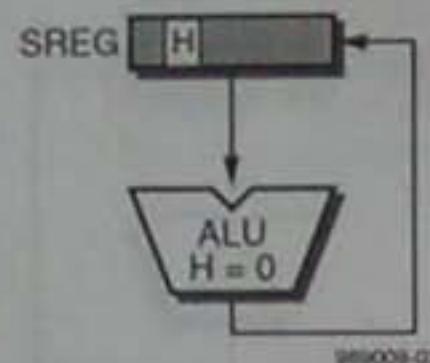

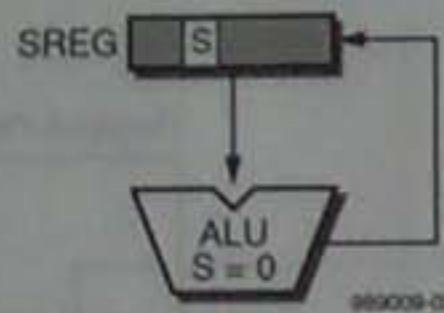

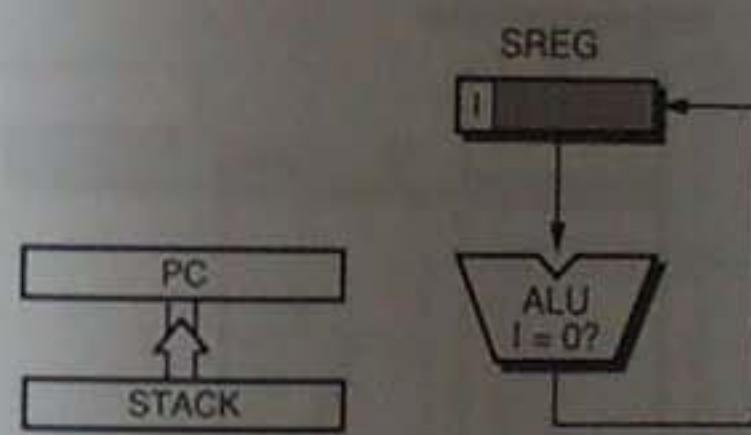

BCLR bit

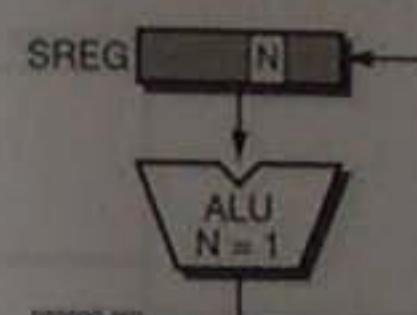

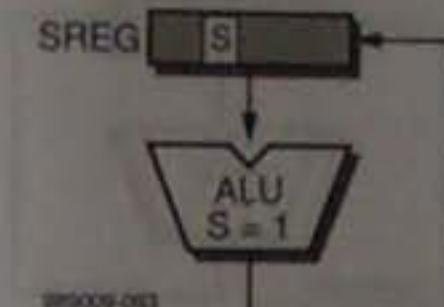

BCLR bit

Lösche ein Bit im STATUS-Register.

Funktion:

$SREG<bit> \leftarrow 0$

Beschreibung:

Löscht das angegebene Bit im STATUS-Register. Der Wert bit kann im Bereich von 0 bis 7 liegen.

Datenfluß:

989009-007

Befehlsablauf:

1 Wort, 1 Maschinenzzyklus, 1 Taktimpuls;

125 ns bei 8 MHz

Flags:

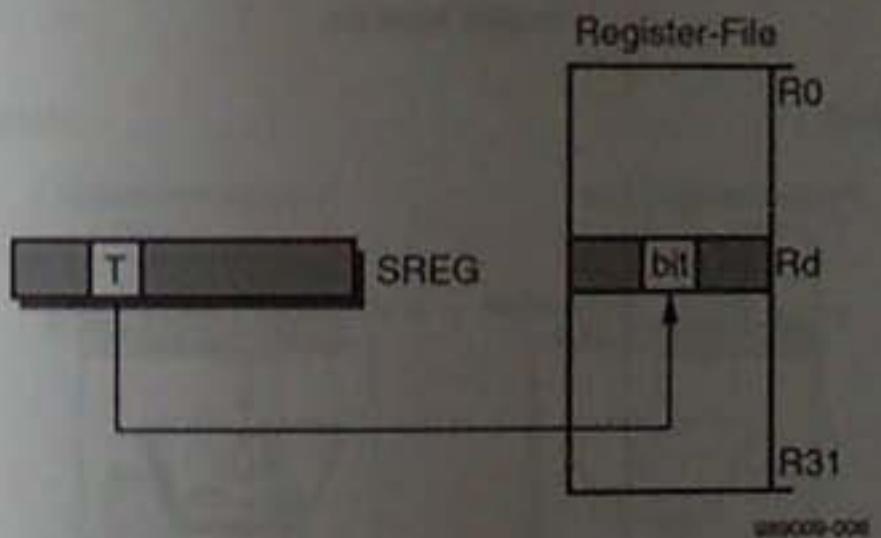

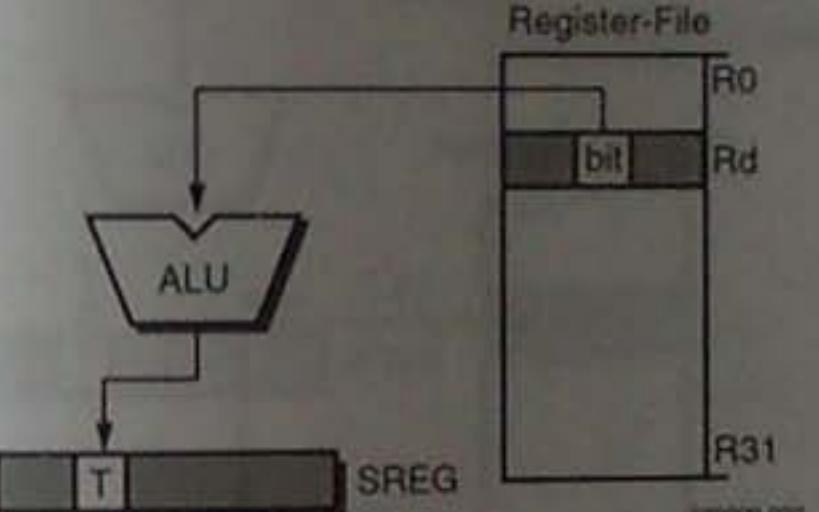

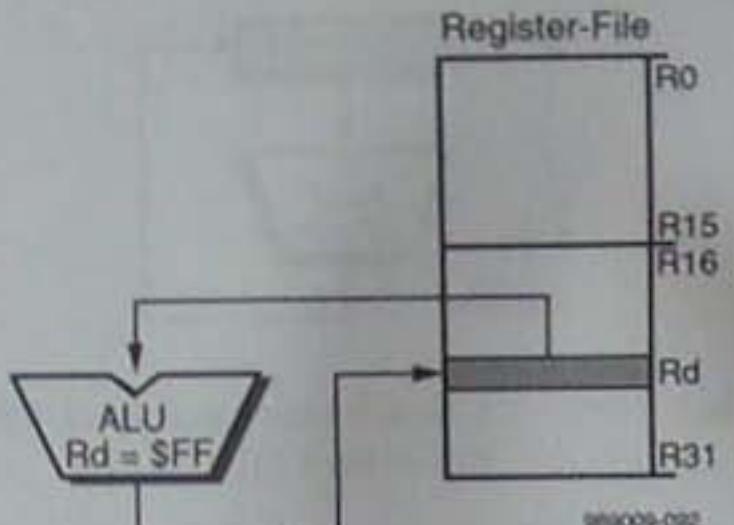

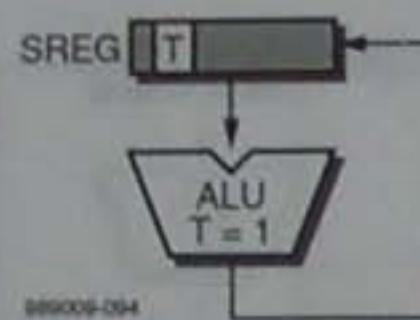

BLD Rd,bit

Lade T-Flag in das Register Rd.

BLD Rd,bit

Funktion:

$Rd<bit> \leftarrow T$

Beschreibung:

Das Transfer-Bit aus dem STATUS-Register SREG wird in die Position bit des Registers Rd geladen. Der Zustand des Transfer-Bits wird nicht geändert. Mit dem Wert bit lässt sich jedes Bit im Register Rd adressieren. Der Befehl ist für alle Register R0 bis R31 im Register-File zulässig.

Datenfluß:

989009-008

Befehlsablauf:

1 Wort, 1 Maschinenzzyklus, 1 Taktimpuls;

125 ns bei 8 MHz

Flags:

|                 |                 |                                                                                                                                                                                                                                                                                                                                                                                      |                 |                                                               |                                                                                                                                                                                                                                                                                                                                                                                     |   |   |   |   |   |        |  |                                                                                                                     |   |   |   |   |   |   |   |   |

|-----------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|---------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---|---|---|---|--------|--|---------------------------------------------------------------------------------------------------------------------|---|---|---|---|---|---|---|---|

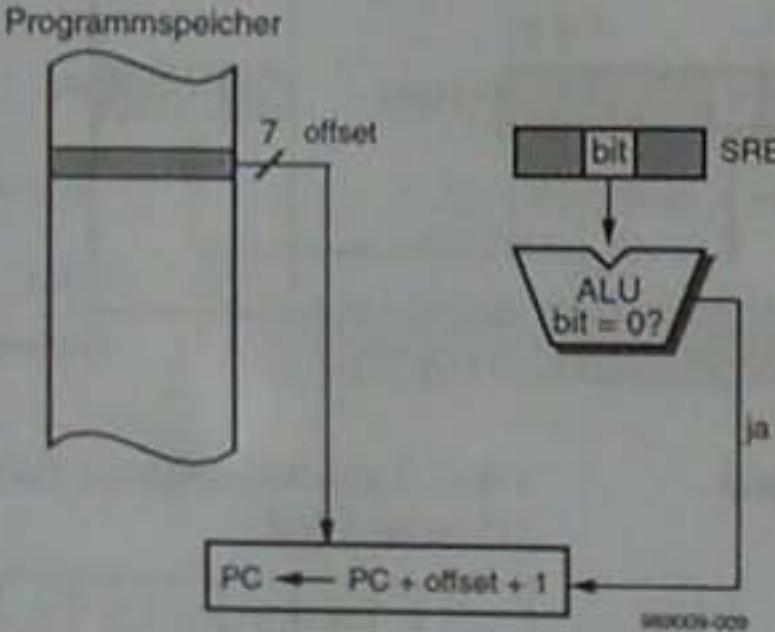

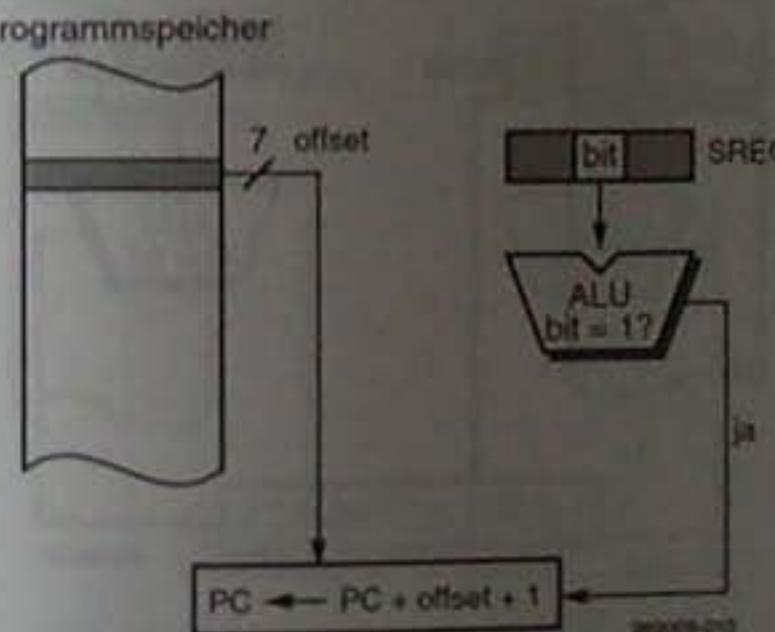

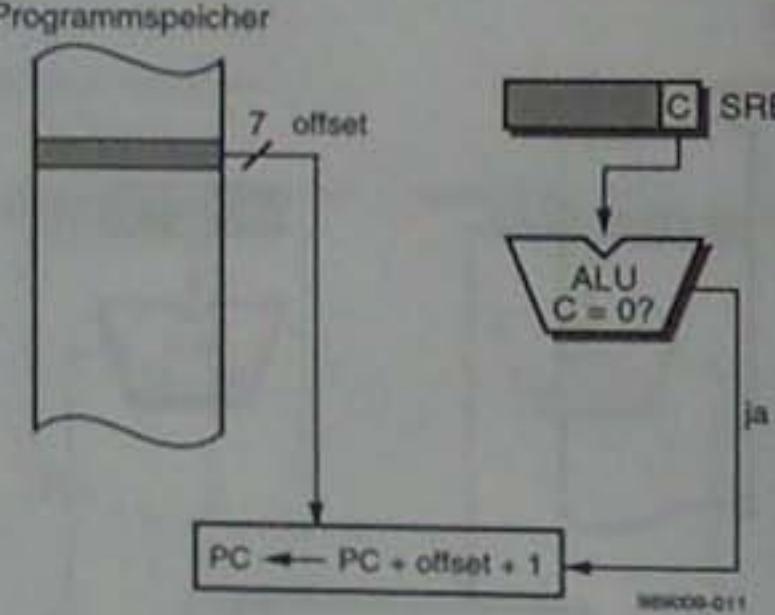

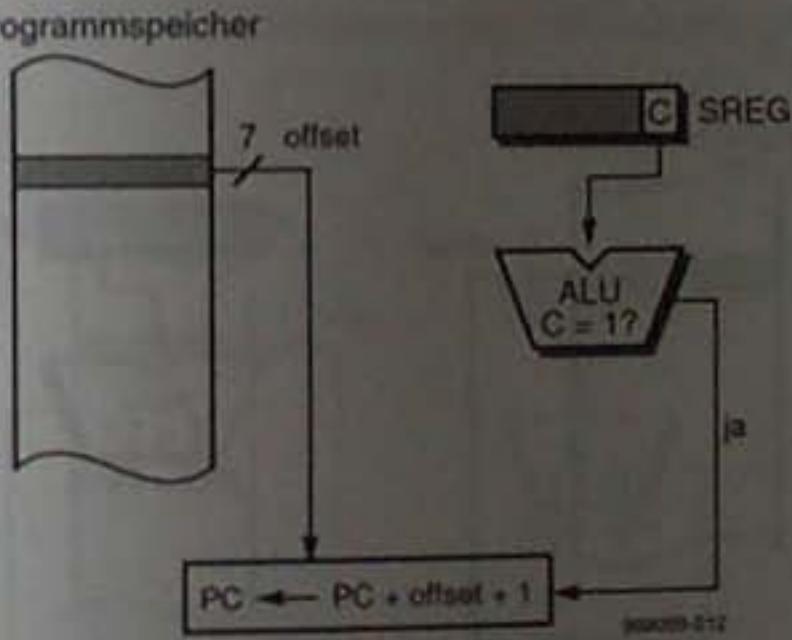

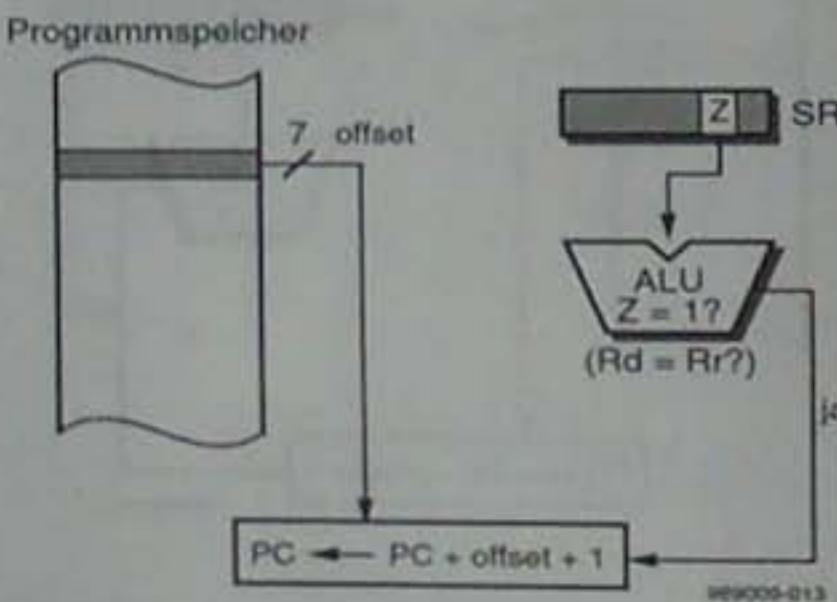

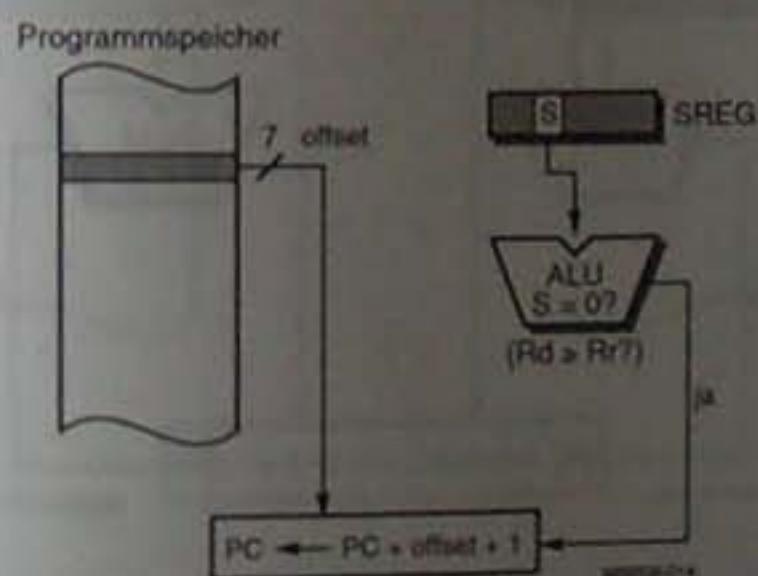

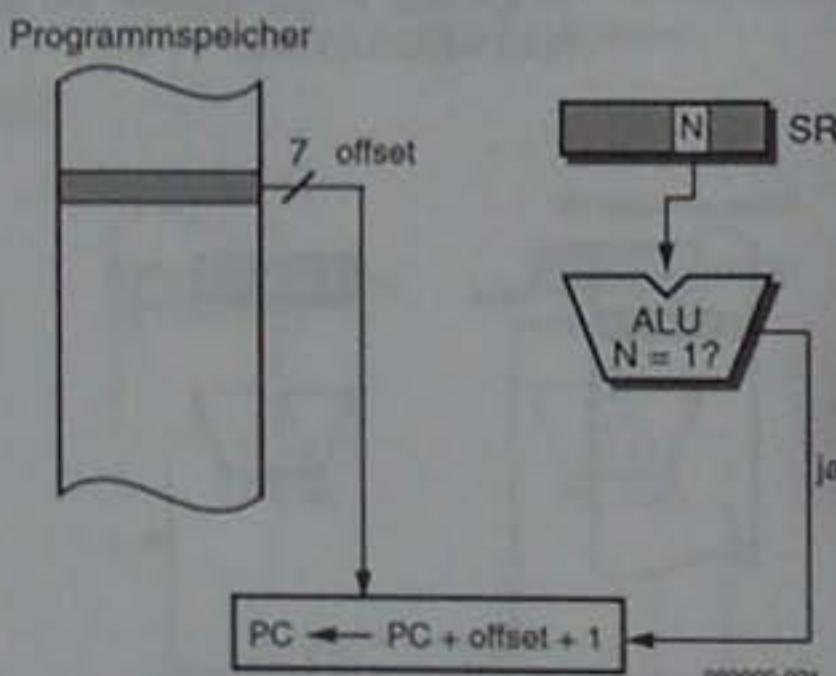

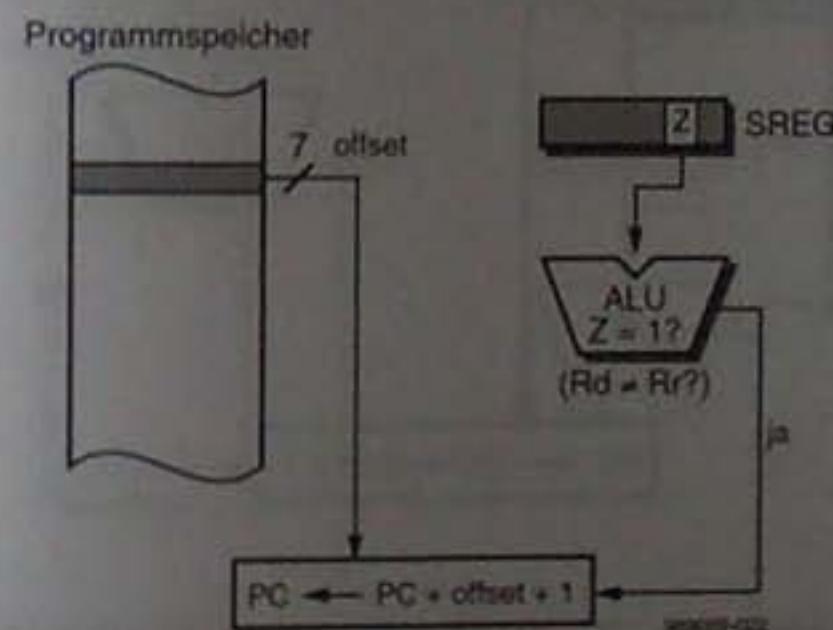

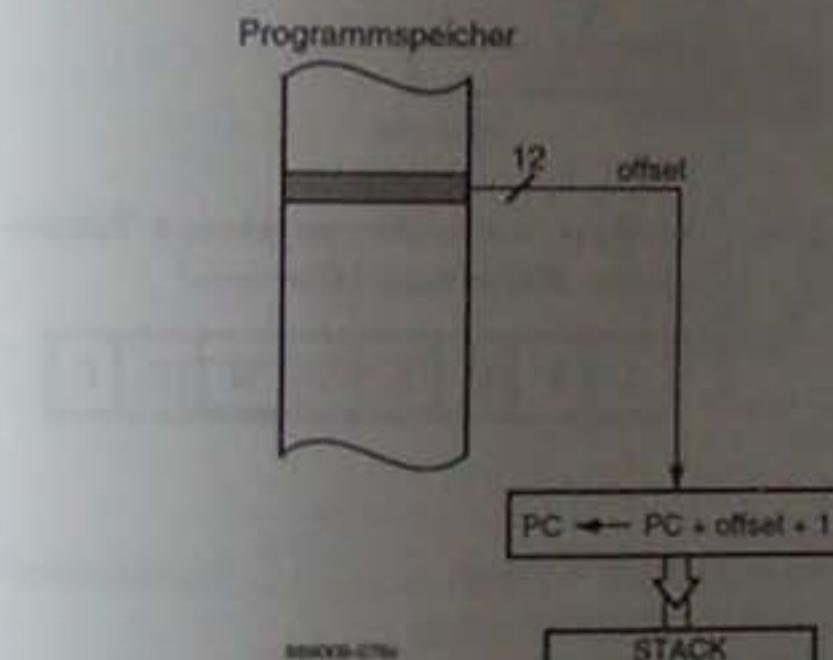

| BRBC bit,offset | BRBC bit,offset | Springe relativ um den Wert offset falls bit im SREG gelöscht.                                                                                                                                                                                                                                                                                                                       | BRBS bit,offset | Springe relativ um den Wert offset falls bit im SREG gesetzt. | BRBS bit,offset                                                                                                                                                                                                                                                                                                                                                                     |   |   |   |   |   |        |  |                                                                                                                     |   |   |   |   |   |   |   |   |

| Funktion:       |                 | $PC \leftarrow PC + 1 + \text{offset}$ , falls $SREG<\text{bit}> = 0$                                                                                                                                                                                                                                                                                                                | Funktion:       |                                                               | $PC \leftarrow PC + 1 + \text{offset}$ , falls $SREG<\text{bit}> = 1$                                                                                                                                                                                                                                                                                                               |   |   |   |   |   |        |  |                                                                                                                     |   |   |   |   |   |   |   |   |

| Beschreibung:   |                 | Ein relativer Sprung um den Wert offset wird ausgeführt, falls ein einzelnes Bit des STATUS-Register SREG an der Position bit gelöscht ist. Mit dem Wert bit läßt sich jedes Bit im STATUS-Register adressieren. Der Wert offset wird als Zweierkomplement interpretiert, so daß relative Sprünge im Bereich von -64 bis +63 relativ zum Programmzähler PC ausgeführt werden können. | Beschreibung:   |                                                               | Ein relativer Sprung um den Wert offset wird ausgeführt, falls ein einzelnes Bit des STATUS-Register SREG an der Position bit gesetzt ist. Mit dem Wert bit läßt sich jedes Bit im STATUS-Register adressieren. Der Wert offset wird als Zweierkomplement interpretiert, so daß relative Sprünge im Bereich von -64 bis +63 relativ zum Programmzähler PC ausgeführt werden können. |   |   |   |   |   |        |  |                                                                                                                     |   |   |   |   |   |   |   |   |

| Datenfluß:      |                 |                                                                                                                                                                                                                                                                                                  | Datenfluß:      |                                                               |                                                                                                                                                                                                                                                                                                |   |   |   |   |   |        |  |                                                                                                                     |   |   |   |   |   |   |   |   |

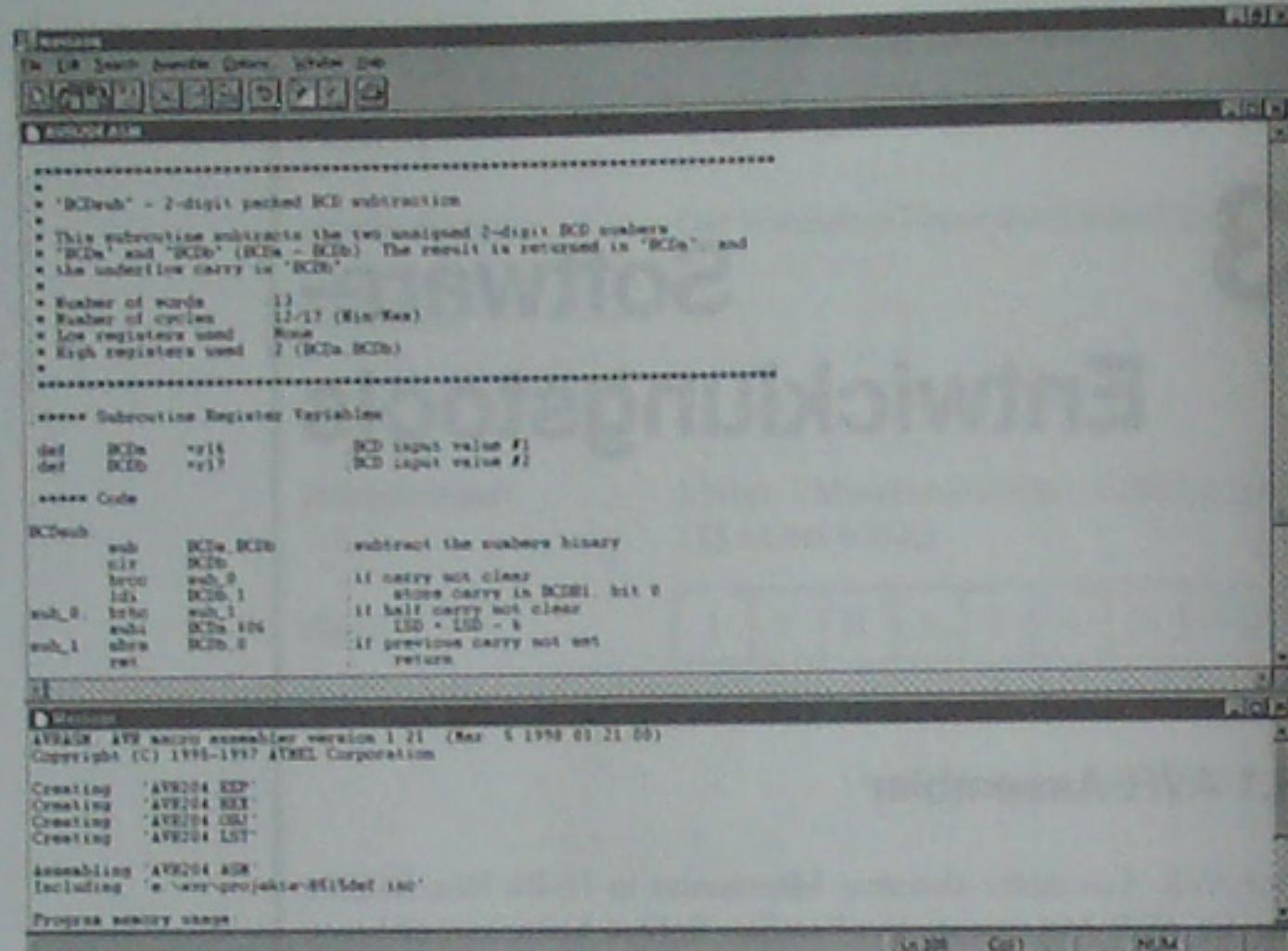

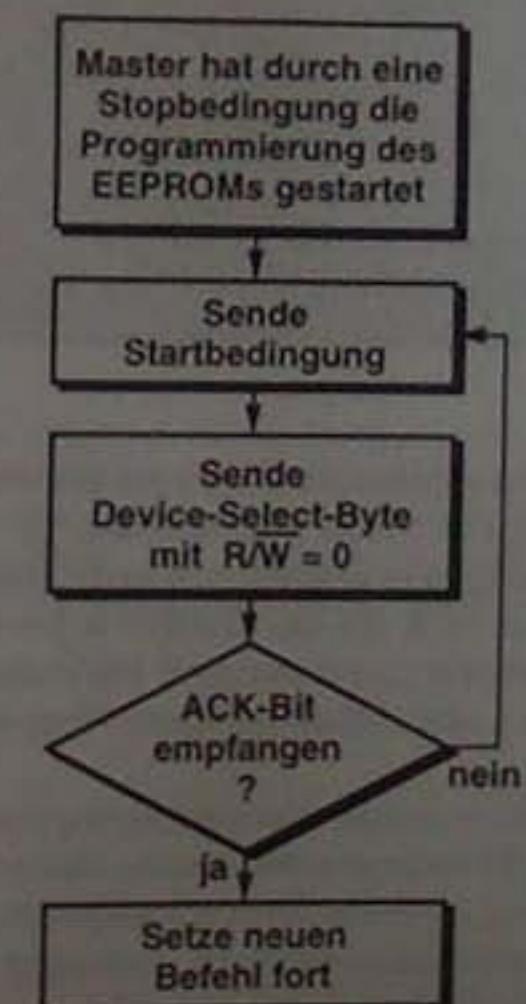

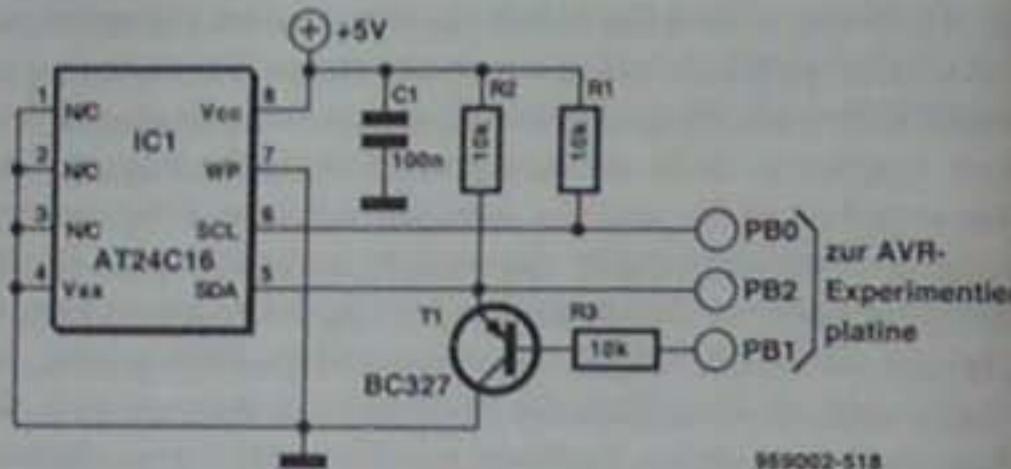

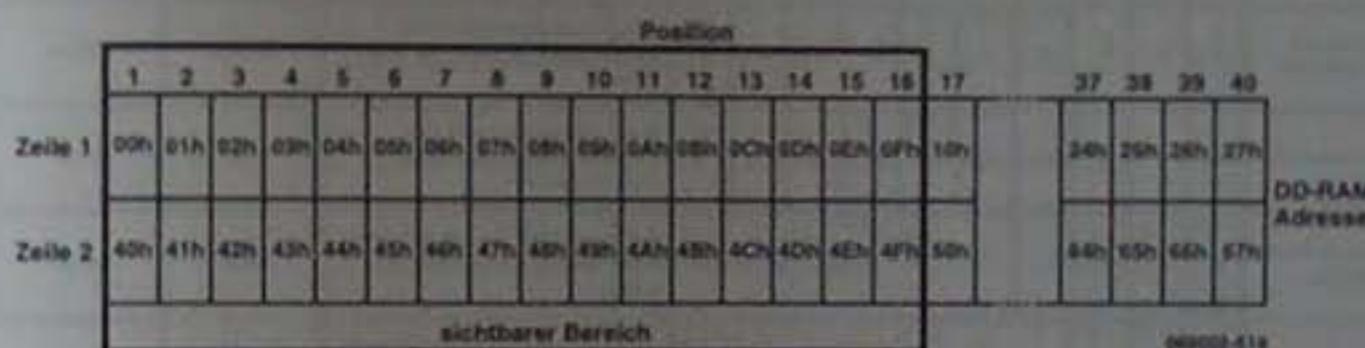

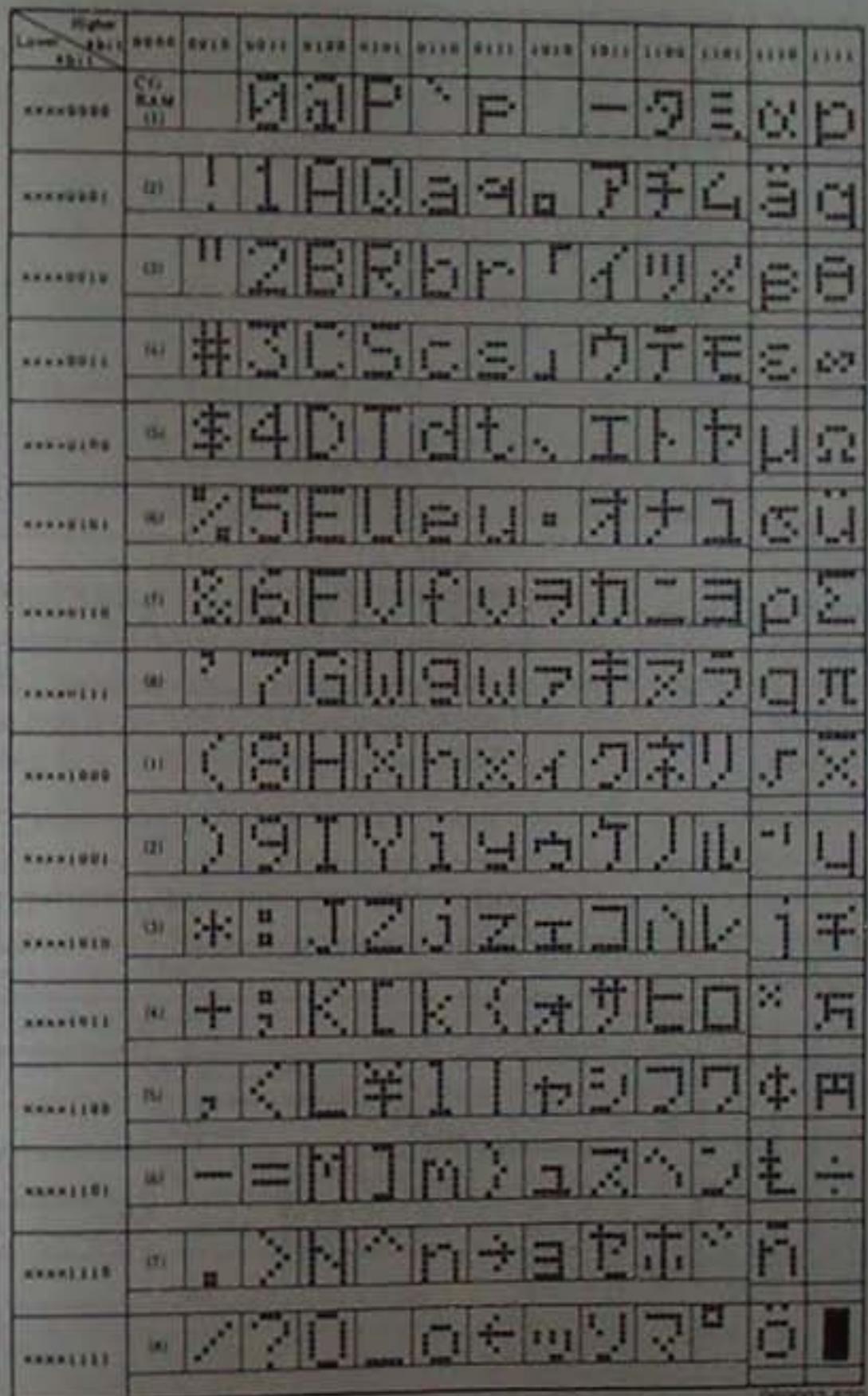

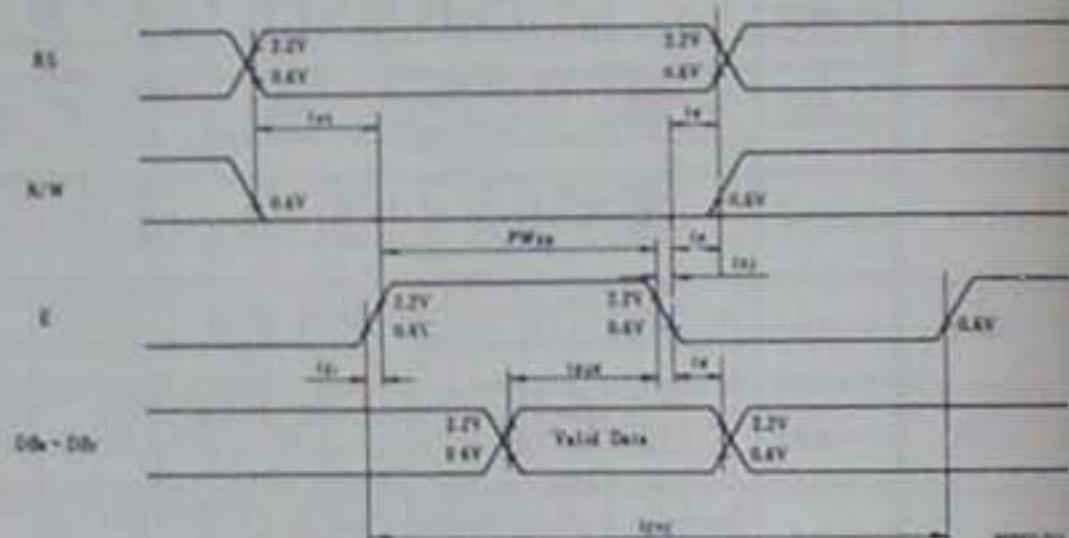

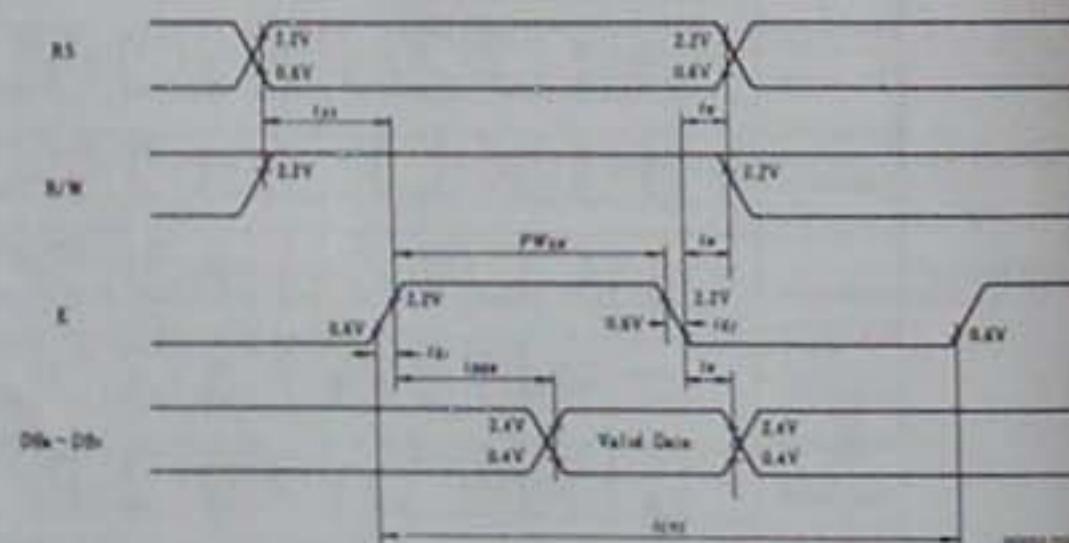

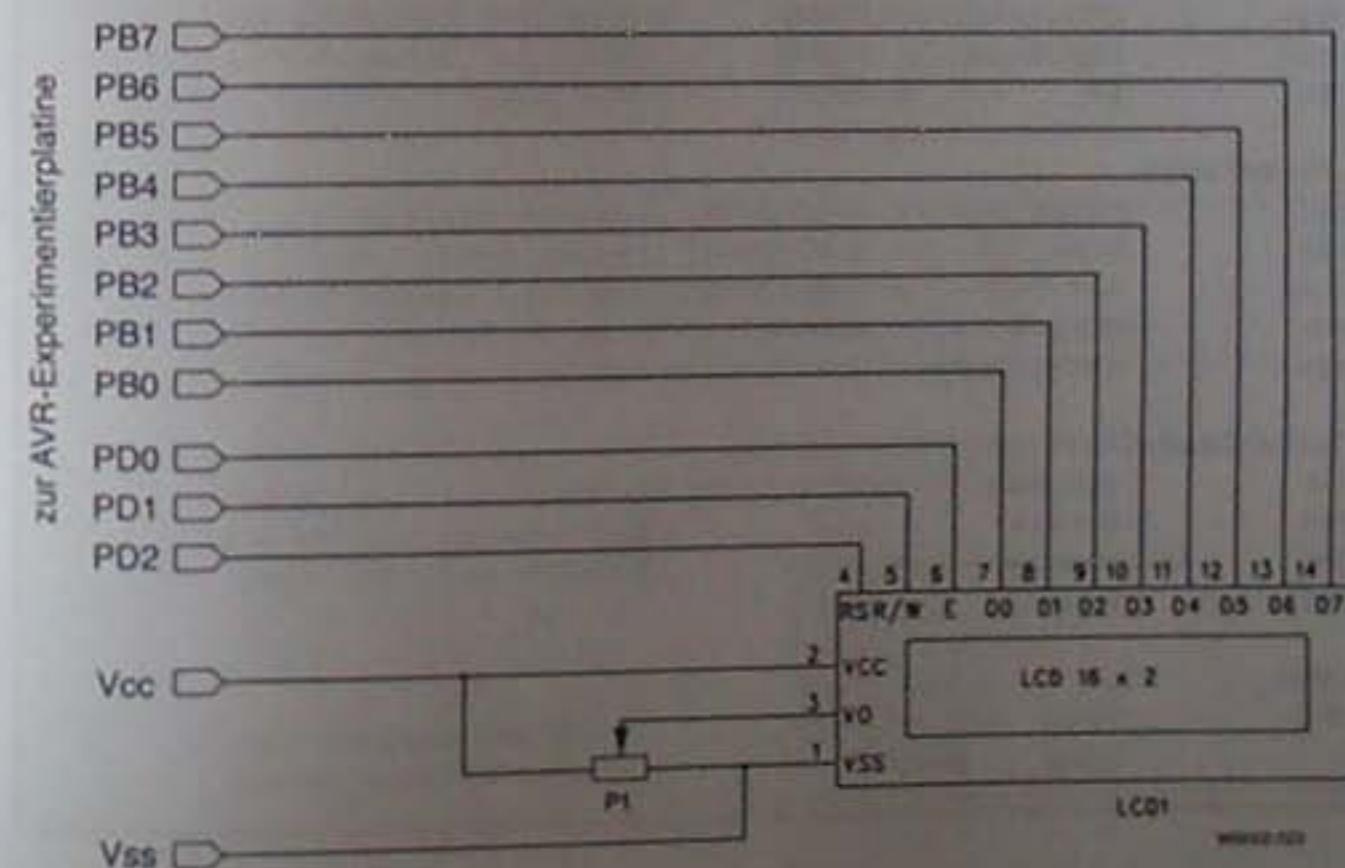

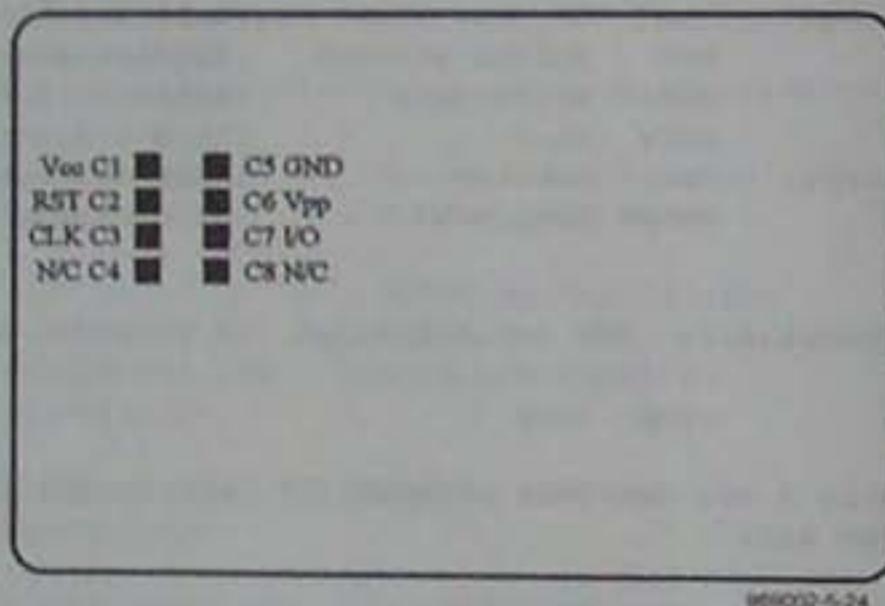

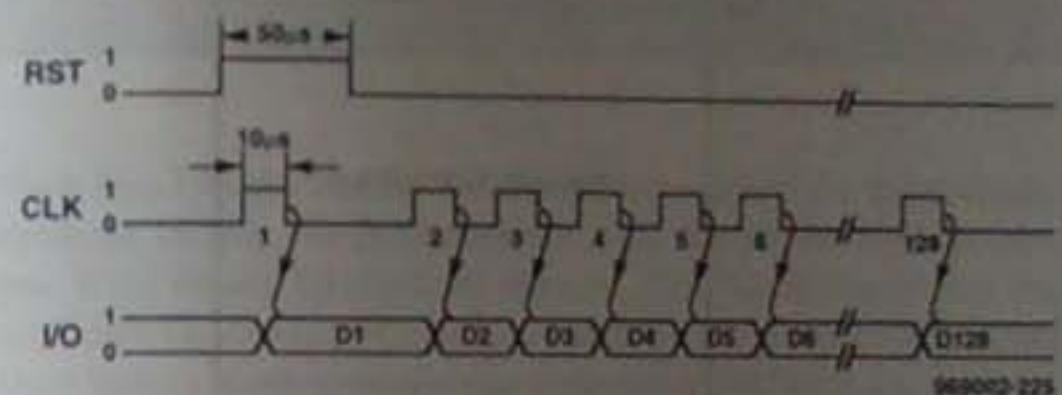

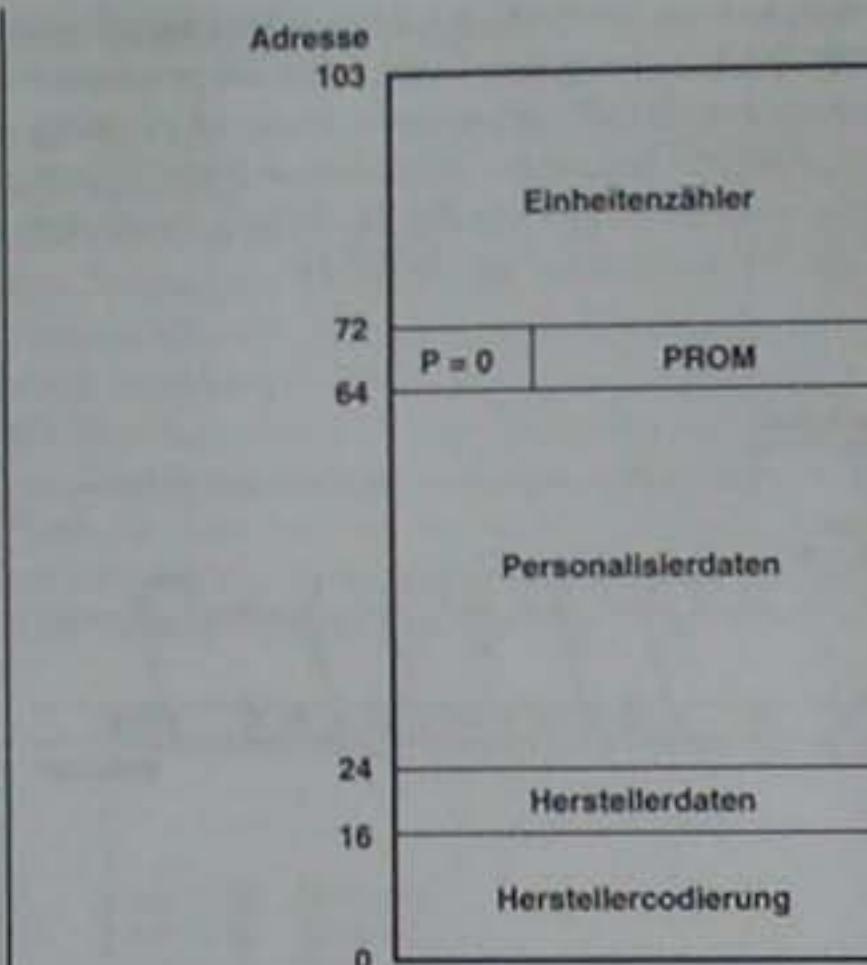

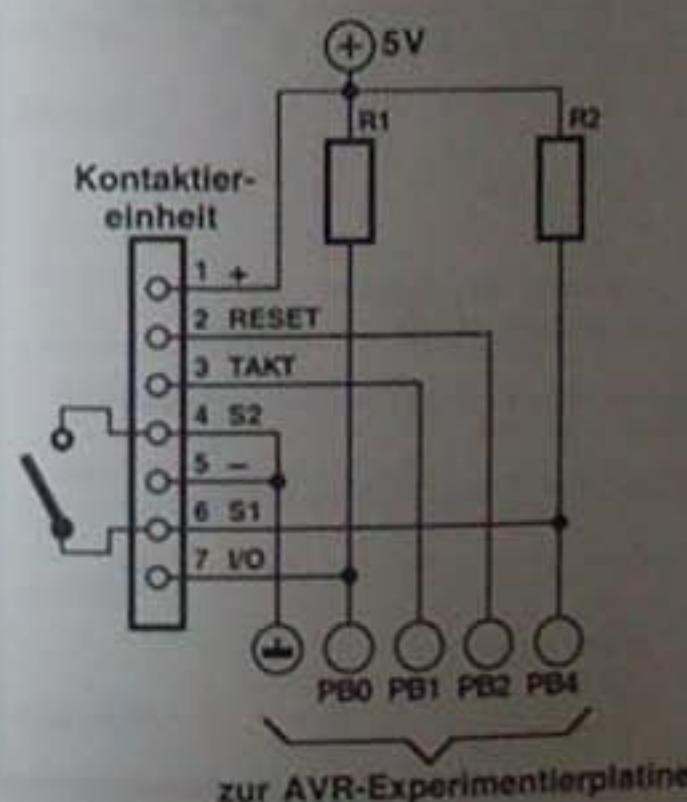

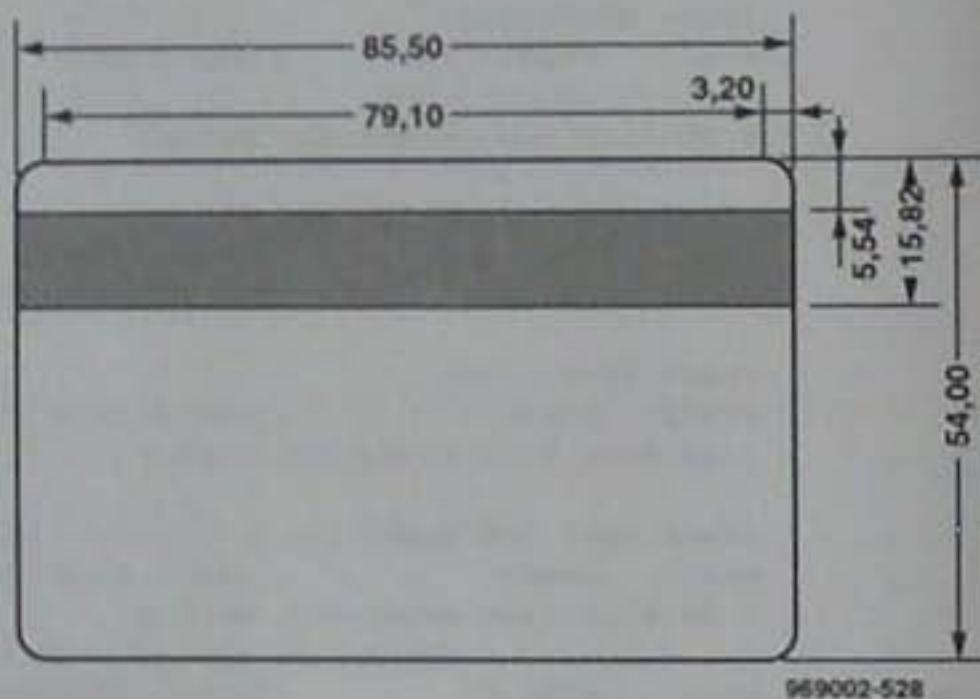

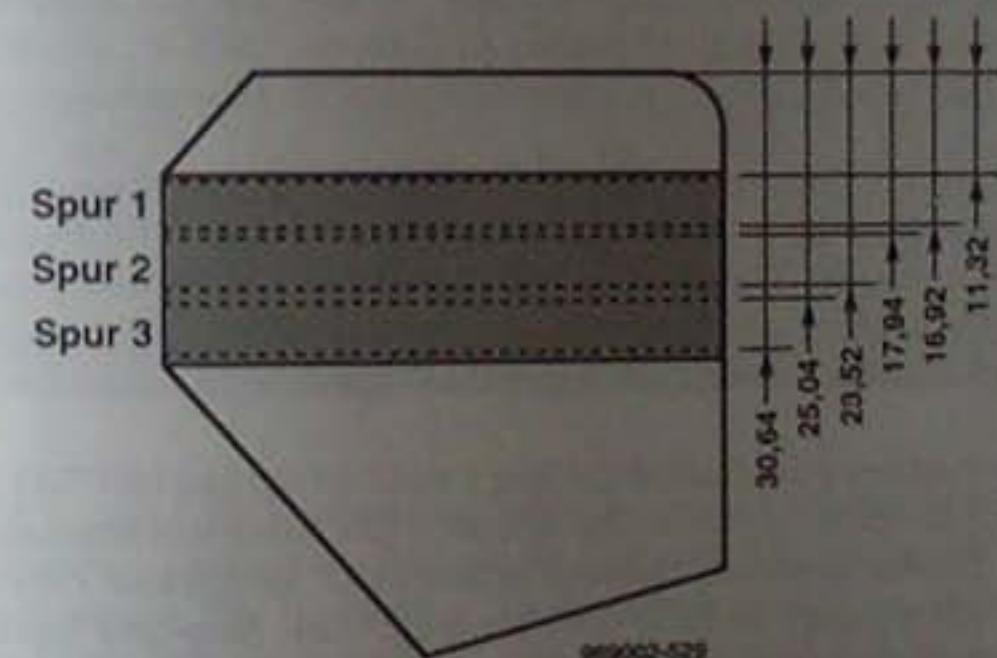

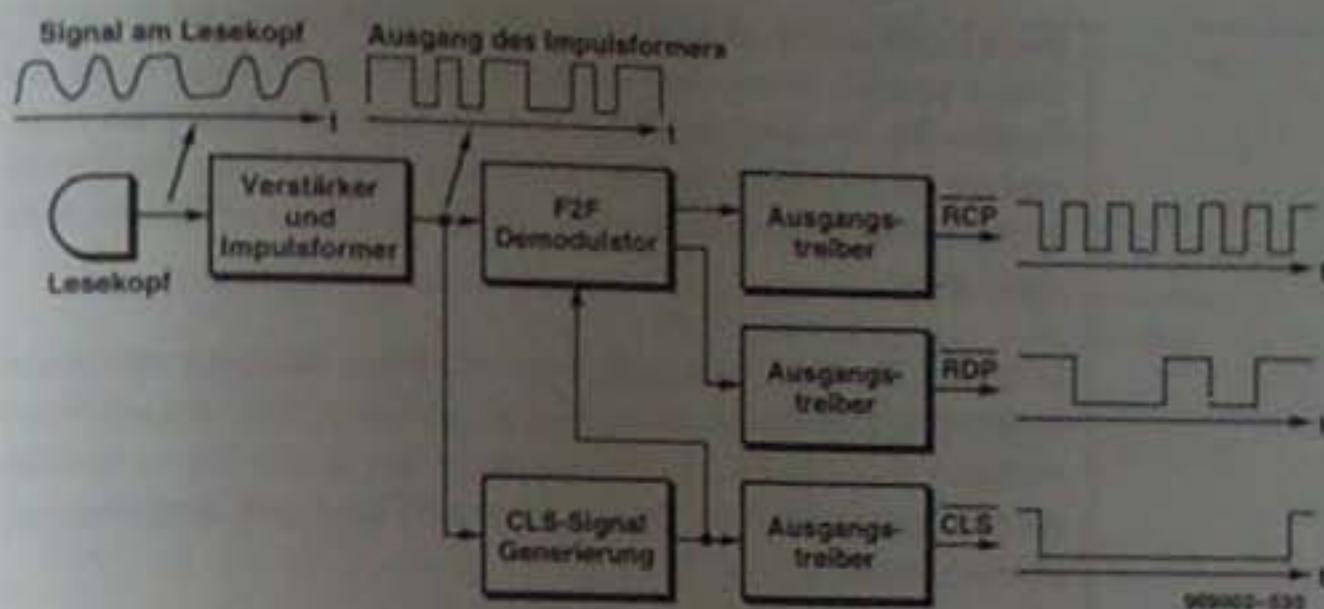

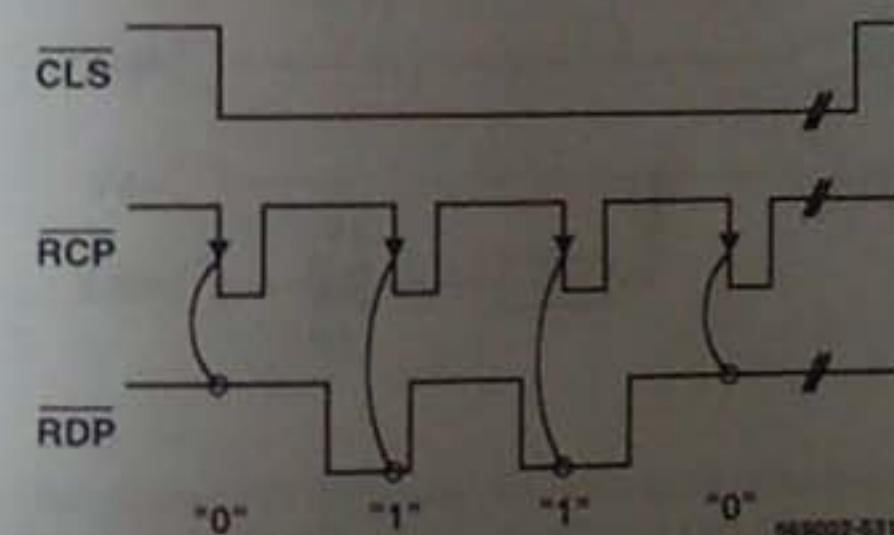

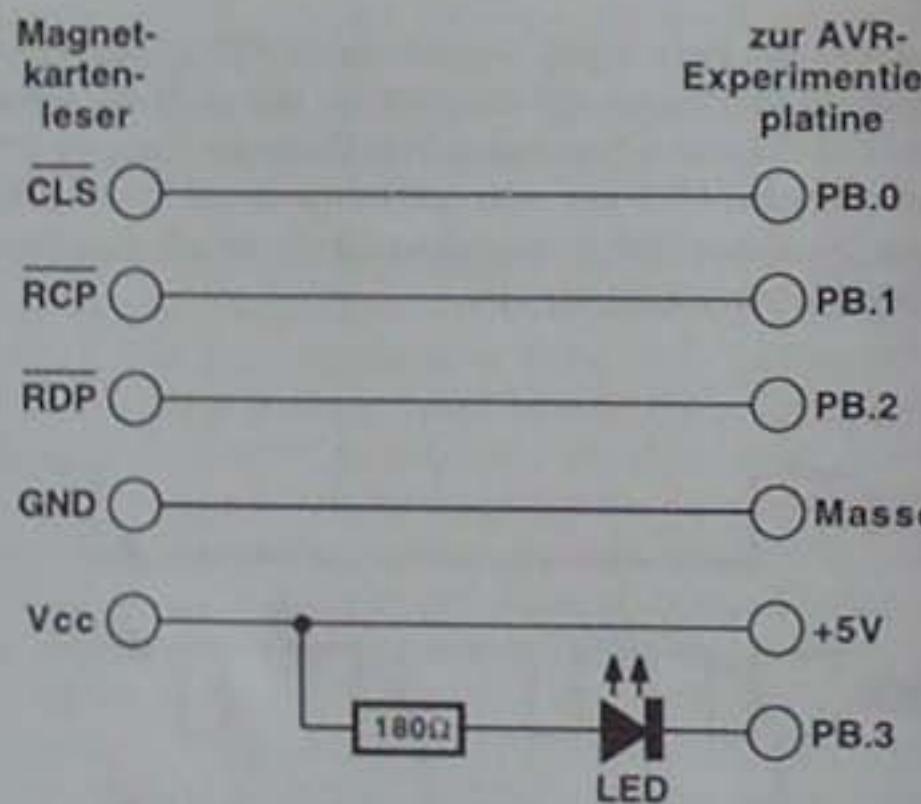

| Befehlsablauf:  |                 | 1 Wort, 1 Maschinenzzyklus (2 bei Sprung),<br>1 Taktimpuls (2 bei Sprung):<br>125 ns (250 ns bei Sprung) bei 8 MHz                                                                                                                                                                                                                                                                   | Befehlsablauf:  |                                                               | 1 Wort, 1 Maschinenzzyklus (2 bei Sprung),<br>1 Taktimpuls (2 bei Sprung):<br>125 ns (250 ns bei Sprung) bei 8 MHz                                                                                                                                                                                                                                                                  |   |   |   |   |   |        |  |                                                                                                                     |   |   |   |   |   |   |   |   |