# Practical Spread Spectrum: Achieving Synchronization with the Slip-Pulse Generator

By Andre Kesteloot, N4ICK ARRL Technical Advisor 6800 Fleetwood Road McLean, VA 22101

two-way, spread-spectrum contact was successfully conducted in January 1988 as part of a continuing series of experiments in spread-spectrum communications administered by the Amateur Radio Research and Development Corporation (AMRAD). This article describes the experiment and the equipment used. Before detailing the experiment, a brief introduction to direct-sequence spread-spectrum (DSSS) communications is in order.

## Direct-Sequence Spread-Spectrum Communications

The RF bandwidth of conventional Amateur Radio modulations (AM, NBFM, FSK) is usually proportional to the amount of information that is transmitted. The bandwidth of the RF signal is kept as narrow as possible (you generally think of narrow contiguous channels), possibly a few kilohertz wide, with each channel containing separate information. When a conventional channel is in use, it is impossible for other users to transmit on the same channel without creating interference.

Using DSSS techniques, you can have a wide RF bandwidth—possibly several megahertz wide—and different networks can transmit on the same frequencies without interfering with one another. Also, the bandwidth of the signal is not related to the information rate.

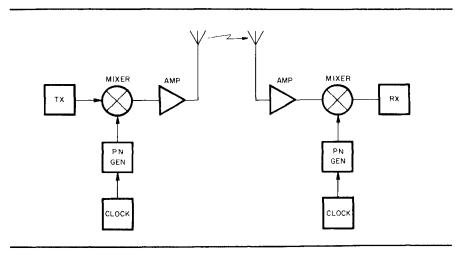

At the DSSS transmitting site, a carrier is mixed with the output of a pseudorandom noise (PN) generator to spread the information over a wide bandwidth. The same pseudo-random sequence is reintroduced in the receiver (see Fig 1). If the original carrier is frequency modulated (to transmit voice, for instance), the original modulation information can be extracted at the receiver. If data other than voice is sent, this data can be logically xored with the PN sequence at the transmitter, and similarly recovered at the receiver.1 In either case, only the signals corresponding to the original PN sequence are correlated at the receiving

Fig 1—Block diagram of a direct-sequence spread-spectrum communications system.

site. The noise is spread over a wide bandwidth and filtered out. The signal-tonoise improvement thus derived, called process gain, is an important derivative of the DSSS process.

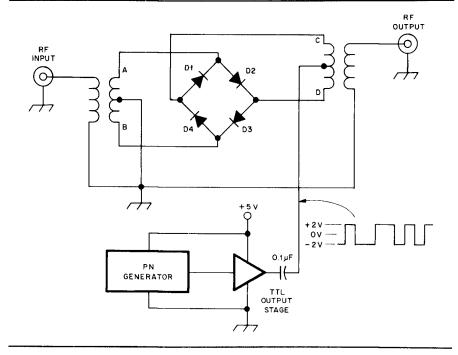

#### The Doubly Balanced Mixer

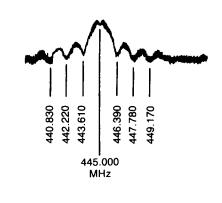

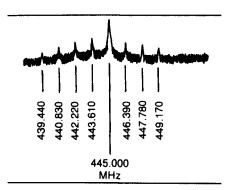

Fig 2 shows the schematic of a doubly balanced mixer used to mix the carrier signal and the output of the PN generator. Note that D1 through D4 are connected as a ring-modulator. The RF carrier is fed to the input transformer, while the PN signal is fed to the center tap of the output transformer. The PN generator uses TTL ICs, and by connecting it via a capacitor, the center tap of the output transformer swings from +2 V to -2 V, with respect to the center tap of the input transformer. When +2 V is applied, D1 and D3 conduct, and D2 and D4 are reversebiased, connecting point A to C, and point B to D. When the output of the TTL goes low, the center tap of the output transformer goes to -2 V. At this instant, D2 and D4 conduct, connecting point A to D and point B to C. This produces a succession of 180-degree phase reversals of the RF carrier at the output, effectively canceling the carrier. The PN signal, which is fed in opposing phase to the input and output windings, also cancels. On the other hand, sidebands are created because of the heterodyne process. Since the output of our PN generator is a square wave in the time domain, its Fourier transform in the frequency domain is a (sin x/x) waveform. Because we are dealing with a signal proportional to the output power of the mixer stage, what we see on a spectrum analyzer connected to the output is proportional to the square of the voltage, or (sin x/x)2 (see Fig 3). As shown in the waveform of Fig 3, the original 445-MHz signal is spread over almost 10 MHz. In practice, a suitable filter shapes the transmitter output to allow radiation of only the main lobe. (The main lobe contains approximately 95% of the total

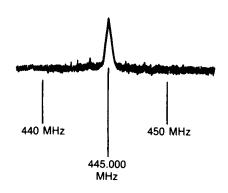

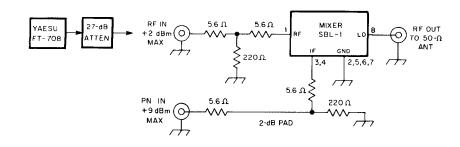

At the receiving site, a similar doubly balanced mixer arrangement recreates, or "despreads," the original carrier (Fig 4). To maximize isolation between ports, each port must be properly terminated in 50-ohm loads. The setup used at both the transmitting and receiving ends is shown in Fig 5.

#### **Synchronization**

To despread a signal, the PN sequence

<sup>1</sup>Notes appear on page 11.

Fig 3—Output of the doubly balanced mixer at the transmitting site. The signal is spread over several megahertz, where  $F_{carrier} = 445$  MHz and  $F_{clock} = 1.390$  MHz.

Fig 2—The doubly balanced mixer. Its function is to combine the carrier signal with the output of the PN generator.

Fig 4—Output of the doubly balanced mixer at the receiving site. The signal is "despread."

Fig 5—Schematic of the doubly balanced mixer port termination at the transmitting site.

at the receiver must be synchronized in both frequency and phase with that of the transmitter. Synchronization is considered to be the most difficult problem to solve in spread-spectrum applications.<sup>2</sup>

There are several ways to achieve synchronization: (1) recover the transmitter clock at the receiving site (a considerable undertaking at 445 MHz), (2) transmit the clock separately, (3) transmit the clock as part of the signal, or (4) synchronize both transmitter and receiver to an external reference, an approach suggested by William Sabin, WØIYH.<sup>3</sup>

The latter technique is used in this

experiment, and the equipment required to extract a stable clock pulse from an AM radio station is described in an earlier article. Thus, the PN generator for both the transmitter and receiver are clocked at the same frequency. The remaining problem is for the two PN sequences to operate in phase.

The station setup used for the successful spread-spectrum QSO is shown in Fig 6. Although the actual QSO was conducted at 445 MHz, some of the preliminary work was performed at 146 MHz. At 146 MHz, the output of the transmitting equipment was connected via a cable to the receiving gear. At 445 MHz, actual

antennas were used at both transmitting and receiving sites. Since the equipment designed for this experiment is not frequency specific, the operation of the synchronization arrangement was exactly the same in both cases.

Referring to Fig 6, the transmitter used was a Yaesu hand-held FT-208R for 146 MHz and an FT-708R for 445 MHz. At the receiving site, I used a Yaesu FT-23R for 146 MHz and an ICOM IC-4AT for 445 MHz. The output of the transmitter and the output of the PN generator are fed to a doubly balanced mixer, as explained earlier, and the signal at the output of the mixer looks like that of

Fig 6—General equipment arrangement for the DSSS experiment.

Fig 3. To decode the original FM modulation at the receiving site, the signal must be despread. (This happens only when the two PN generators are in phase.)

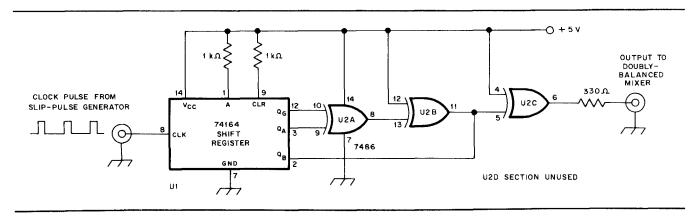

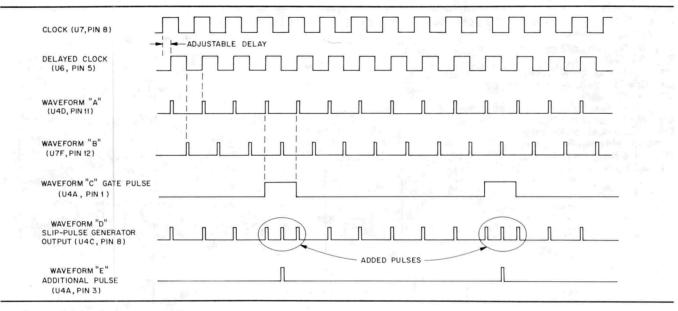

To understand how the phasesynchronization process works, imagine that the two PN generators are receiving the same 1.390-MHz external clock pulse. These pulses, at both sites, are used to clock identical 7-stage PN generators (Fig 7).5 Although the two PN generators are identical, their sequences are not necessarily in phase because they may have been started or reset at different times. To obtain phase synchronization, it is necessary to shift the phase of the receiver's PN generator, with respect to that of the transmitter's, until the two sequences coincide. To that effect, the slip-pulse generator occasionally introduces an extra pulse in the 1.390-MHz clock stream. Thus, the receiver's PN generator slowly "catches up" with the transmitter's until coincidence is achieved. When this happens despreading takes place, the receiver's squelch opens, and the slip-pulse generator inhibits the introduction of additional slip pulses.

#### **Circuit Description**

To achieve phase synchronization, I used the built-in DTMF (dual-tone multifrequency) generator of the Yaesu FT-208R/708R to send a "1." I also prewired U1, an SSI-202 DTMF decoder, in the slip-pulse generator to accept a "1" as a valid output (see Fig 8).

Let's assume that the two PN sequences are not in phase. There is no

despreading and thus no output from the receiver. The slip-pulse generator continues to insert pulses at a very slow rate. Since a 7-stage PN register is 127 steps long, after a maximum of 126 additional slip pulses, there will be a moment when the two PN sequences are in phase. At that moment, despreading takes place, the squelch opens, and the receiver generates a "1" that is recognized by U1. The green LED illuminates and the resetset (R-S) flip-flop (U2A and U2B) latches, turning on the red LED and grounding pin 4 of U4B.

U3, a 555, free-runs at about 200 Hz. If U4B is enabled (ie, when there is an absence of a valid DTMF signal), U3's output pulses are channeled to U5. U5 is a 7474 connected in a one-and-only-one configuration.

Fig 7—Schematic of the pseudo-random noise generator. U1—74164 8-bit shift register.

U2-7486 quad 2-input xon gate.

Fig 8—Schematic of the slip-pulse generator. Circled letters reference the waveforms shown in Fig 9. Q1, Q2, Q3-2N2222 NPN transistor. S1, S2-SPST switch. U1—SSI-202 DTMF decoder. U2—CD4011 quad 2-input NAND gate. U3-LM555 timer. U4—7400 quad 2-input NAND gate. U5—7474 dual D flip flop. U6-74123 dual retriggerable **≶** 390 390 390 monostable multivibrator. U7—7414 hex Schmitt trigger. Y1—3.58-MHz crystal. POWER DS3 ≥1.2 k DS1 LOCK T 104148 TO RX SPKR TERMINALS SSI - 202 Q2 01 2N2222 DTMF DECODER 0.01 €2.2 k 2.2 k 2.2 k U2A  $\odot$ CD4001 HOLD 0.01 **S2** TO EXTERNAL SPKR 0.001 U2B Fبر 1.5 16 V S1 RESET ENABLE : HIGH 1 k FREQ ADJ RESET IN4148 U3 LM555 TIMER U4B 0.001 R2 100 k 22 k 7474 4 OUT 4µF 2.2 16 V SLIP U5A U5B PULSE D F-F D F-8 7414 **☆ 0.1** EXCEPT AS INDICATED, DECIMAL VALUES OF CAPACITANCE ARE IN MICROFARADS (  $\mu$ F); OTHERS ARE IN PICOFARADS ( pF); RESISTANCES ARE IN OHMS; k = 1000, M = 1000 000. Л CLOCK T = TANTALUM \* = MICA U6A 74123 DUAL MONOSTABLE MULTIVIBRATOR PHASING 50 k R<sub>EXT</sub> 20 CEXT JL. 100 \* B 680 USB JL (A) E Q3 2N2222 0 150 × J \_\_\_\_\_ U7C O)output DELAYED

Fig 9—Slip-pulse generator timing sequence.

The external clock signal is applied to U6A and U6B, two monostable multivibrators connected in series. This circuit provides an adjustable delay to compensate for TTL gate propagation delays, different cable lengths, and so on. The delayed clock signal is then buffered by U7B and U7C, and fed to U7F and U7E (connected as two "half-monostable" sections that produce a short pulse on the trailing and leading edges of the clock pulse, respectively). The signal from U7E is also used to clock U5. U5 produces a gating signal, the length of which is the interval between two clock pulses, only after it receives a pulse from U3. Whenever this gating pulse occurs, U4A is enabled and allows a pulse synchronized on the trailing edge of the clock (ie, half-way between two regular clock pulses) to reach U4D, where it is added to the normal stream of 1.390-MHz pulses. (A pulse timing diagram is shown in Fig 9.) We have thus "slipped-in" an extra clock pulse for every pulse created by U3 (hence my name for the slip-pulse generator), and the effective clock pulse at the receiver end is 1,390,200.

This process continues as long as U4B remains enabled. A valid DTMF signal inhibits U4B. To prevent further tones or audio noise from adding extra slip pulses once phase synchronization has been achieved, the output of the DTMF decoder is connected to U2A and U2B, an R-S latch, that can only be reset by grounding pin 6 of U2B via S1. Similarly, S2 can simulate the reception of a valid tone by stopping the slip-pulse generator, a help during testing.

#### The Experiment

To facilitate experimentation, various

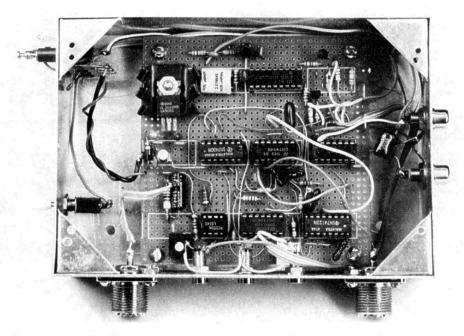

parts of the equipment were built in separate shielded boxes and connected as shown in Fig 6. Fig 10 is a photograph of the slip-pulse generator. I found that at slip-pulse frequencies above 250 Hz, the system cannot achieve lock. This upper limit occurs because it takes a finite time for the receiver's squelch to open and the DTMF decoder to recognize a valid tone. By adjusting R2 so that the output frequency of U3 is about 200 Hz, it took a maximum of 42 seconds for locking to occur reliably. (Depending on the respective position of the two PN sequences, it can take less time; 42

seconds was the maximum time required when the two PN sequences were 126 steps apart.) Once synchronization is achieved, however, both transmitter and receiver clocks remain in phase, whether communication takes place or not. In a regular spread-spectrum system, synchronization must be achieved each time the push-to-talk switch is engaged. In this experiment the transmitting site and the receiving site were symmetrical (no amplifier was connected between either antenna and doubly balanced mixer), and it was possible to establish a two-way contact between the two units. Because

Fig 10-The slip-pulse generator.

of the extremely low power levels used (less than 1 mW), the maximum distance between the transmit and receive antennas was less than 12 inches! (The actual transmitter and receiver were located about 50 feet apart to avoid direct feedthrough from transmitter to receiver.)

Once the two PN sequences are properly phased, adjust the relative phase of the clock pulses. By properly adjusting R1 in the slip-pulse generator, it is possible to match the phase of the transmitter and receiver clock pulses. Fig 4 shows the output of the despread signal when the two clocks are perfectly in phase. Fig 11 shows the same despread signal with the receive clock about 10 degrees out-of-phase.

All parts used for this experiment are readily available. The SSI-202 touch-tone decoder chip is available from Radio Shack® (RS 276-1303), and the doubly balanced mixers were purchased from Mini-Circuit Labs (type SBL-1(6)).6

Fig 11—Output of the doubly balanced mixer at the receiving site. The two clocks are out of phase by about 10 degrees. Here, F<sub>carrier</sub> = 445 MHz and F<sub>clock</sub> = 1.390 MHz

#### Conclusion

Although this experiment worked faultlessly, the equipment is fairly slow to reach synchronization and somewhat

cumbersome, because it relies on the presence of a separate unit to provide synchronizing pulses. This experiment was designed to prove that it is possible to use such a synchronization approach. My thanks go to the core group of AMRAD, particularly Chuck Phillips, N4EZV, Lawrence Kesteloot, N4NTL, and Mike O'Dell, N4NLN.

#### Notes

- A. Kesteloot, "Experimenting with Direct Sequence Spread Spectrum," QEX, Dec 1986,

- <sup>2</sup>R. Dixon, Spread Spectrum Systems, New York,

- Wiley 2nd ed, 1984, p 214.

³W. Sabin, "Spread Spectrum Applications in Amateur Radio," QST, Jul 1983, p 16.

- 4A. Kesteloot, "Extracting Stable Clock Signals from AM Broadcast Carriers for Amateur Spread Spectrum Applications," QEX, Oct 1987, pp 5-9.

5A. Kesteloot, "Practical Spread Spectrum: A

- Simple Clock Synchronization Scheme," QEX, Oct 1986, pp 4-7.

- 6Mini-Circuit Labs, PO Box 166, Brooklyn, NY 11235, tel 718-934-4500

### **Teledyne Semiconductor Markets New Components**

The TSC9405 is a serial input, 16-bit parallel output shift register. It features high-current on-chip data latches and power MOS output drive devices. The part is an ideal serial interface component between microprocessor I/O ports and high-current/voltage peripheral devices. such as LEDs, thermal print heads and relays. The TSC9405 is available in a 24-pin plastic DIP and a 24-pin CerDIP package. Prices start at \$4.75 each for quantities of 100 or more.

The TSC500A is an integrating converter analog processor designed for applications that require high accuracy and low noise, with the added flexibility of microprocessor control. The TSC500A is unique because all measurement functions are microprocessor controlled through two logic input signals.

The TSC500A is an improved version of the TSC500. Improvements allow up to 16 bits of resolution and faster conversion times for lower resolution applications. The component contains all the analog circuitry needed to construct an integrating analog-to-digital converter. The TSC500A operates from

±5 V and has a power dissipation of 10 mW. This device is available in a 16-pin plastic DIP and a 16-pin CerDIP. Surface mount packages are available. Prices in quantities of 100 or more start at \$6.85 each (\$8.22 each for surface mount devices).

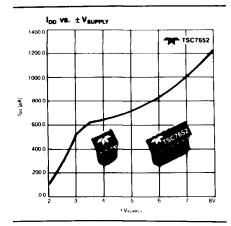

The TSC7652 is a low-noise chopperstabilized op amp that improves noise performance and features an extremely low input-offset voltage for precision in-

strumentation, temperature measuring and medical electronics applications. Input-offset voltage is typically  $\pm 10 \mu V$ over the device's entire temperature range. The TSC7652 is available in a 14-pin plastic package, an 8-pin plastic package, a 14-pin CerDIP package and an 8-pin CerDIP package. Prices in quantities of 100 or more start ar \$4.40 each. For more information on any of these Teledyne Semiconductor devices contact the manufacturer at 1300 Terra Bella Ave, Mountain View, CA 94039-7267, tel 415-968-9241.—Maureen Thompson, KA1DYZ